# -C-SE\_=2021== -C-O-MFUTE-R==-O-R-GANIZATIO-N

|           |               |                |            |                   |              | [C]    |                |           |              |          | Y TO TRI  | レ保の文制な   |    |   |    | 文精なフト社   | またにの !!      |   | の文精なフト     |

|-----------|---------------|----------------|------------|-------------------|--------------|--------|----------------|-----------|--------------|----------|-----------|----------|----|---|----|----------|--------------|---|------------|

| THSTHERU  | A M V O R L D | 0 2 2 0 2 0    | ト社明 をに美と 字 | > 1018, → 11 → 11 | 8-01 × 12-01 | HS YII | 中 び技す 国出のシ品    | 8 215 W O | E0 4 2 4 6 E | の文精なフト社明 |           | ト社明 をに美と | ۶E |   |    | 明をに美と学印び | - U UNASANDO |   | 杜平 をに美と 字印 |

| 2 H H H H | Z III O 14 2  | E -1 (0 H -1 H | 印 ジ技す 国主   | N 124 A           | \$ 21 1 10   | A<br>T | 新 <b>山</b> 异道道 | 4 H - 6   | NT TR        | をに美と学    | N H H H H | AZ AL    |    | G | -V | √?-]\    | Г<br>Г       | 1 | び技す        |

DR

# Agenda

### Topics:

- 1. Basics: Clock, Latches and Flip Flops

- 2. Sequential and Combinational Circuits

### Patterson: Appendix C, Section 4.1, 4.2, 4.3

# This Week in CSE 2021

# Allowed aids for the midterm:

- Green

Sheet

- 8.5 x 11

Cheat

Sheet

| WEEK | WEEK OF | Mon  | Wed      | Lab          | Topic                             |

|------|---------|------|----------|--------------|-----------------------------------|

| 1    | Sep 05  | 8.78 | ~        | -            | Overview of the course            |

| 2    | Sep 12  | V    | ~        | 121          | Performance and Data Translation  |

| 3    | Sep 19  | ~    | ~        | A            | Code Translation                  |

| 4    | Sep 26  | ~    | Quiz #1  | В            | Translating Utility Classes       |

| 5    | Oct 03  | V    | ~        | С            | Translating Objects               |

| 6    | Oct 10  | 1020 | 2        | -            | <b>READING WEEK - No Classes</b>  |

| 7    | Oct 17  | V    | Mid-term | D            | Introduction to Hardware          |

| 8    | Oct 24  | V    | ~        | Make-up Labs | Machine Language + Floating-Point |

| 9    | Oct 31  | ~    | ~        | K            | The CPU Datapath                  |

| 10   | Nov 07  | ~    | Quiz #2  | L            | The Single-Cycle Control          |

| 11   | Nov 14  | ~    | ~        | М            | Pipelining                        |

| 12   | Nov 21  | V    | ~        | N            | Caches                            |

| 13   | Nov 28  | ~    | Quiz #3  | Make-up Labs |                                   |

| 14   | Dec 05  | ~    | -        |              | No lecture on Wednesday           |

Requirements for Cheat, Instruction Sheets (Midterm and Final Exam)

Cheat Sheets MUST:

- Be no larger than 8.5" x 11" in size

- Information MUST be original handwriting NO printed or copied cheat sheets are permitted

- A single sheet, writing permitted on both sides

Green (MIPS Instruction) Sheets:

- MUST be extracted from textbook

- OR you may use a print out of the pdf version from the course web site

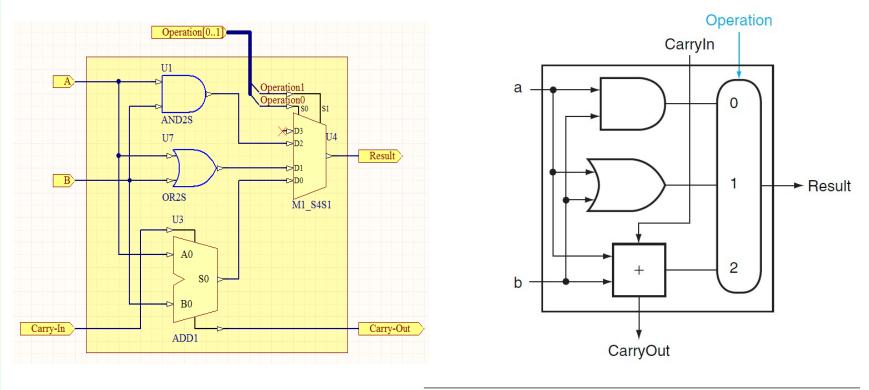

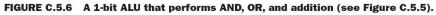

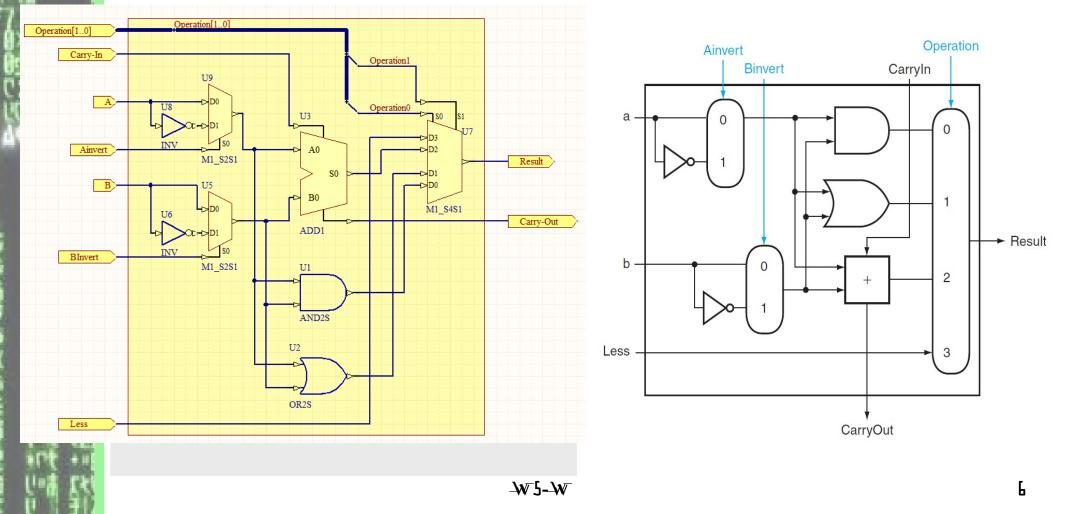

### What is the difference between these two ALUs?

- The 1-bit adder is supplemented with AND and OR gates

- A multiplexer controls which gate is connected to the output

1-bit ALU with AND, OR, and Addition capability

## SLT (and Nor) Logic Added

- The 1-bit adder is supplemented with AND and OR gates

- A multiplexer controls which gate is connected to the output

#### From Last time...

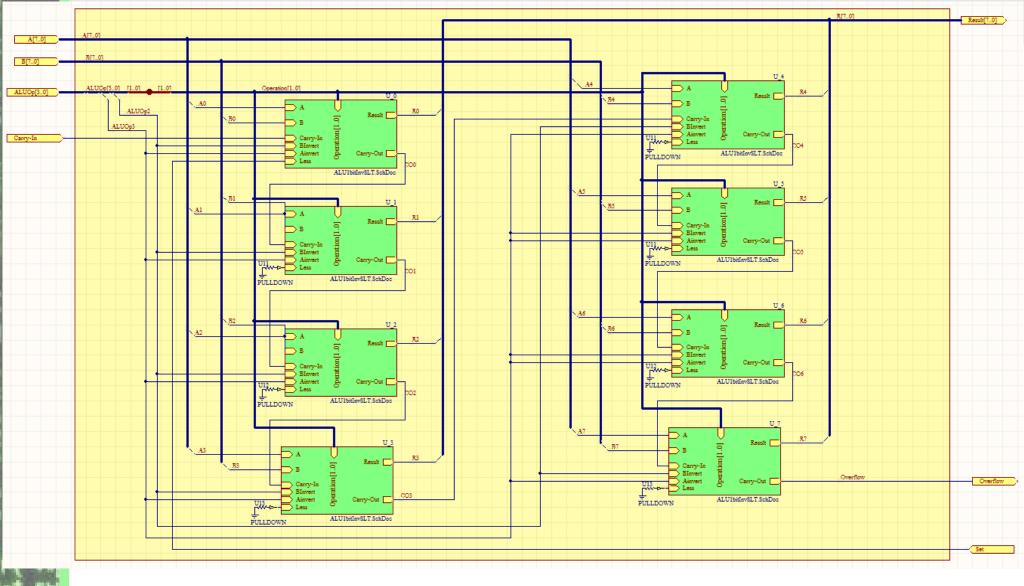

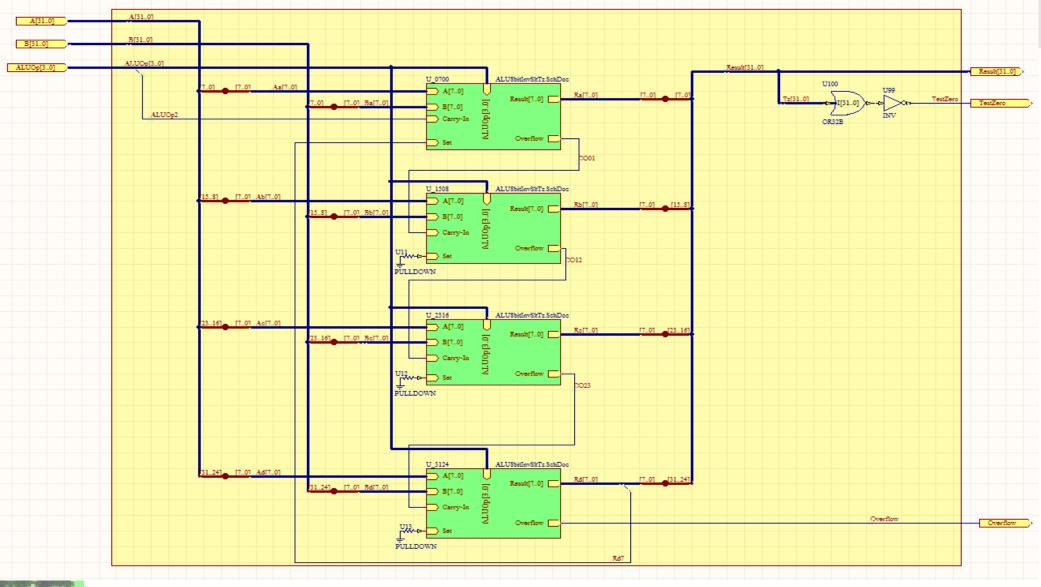

32-bit ALU w/ And, OR, Nor, Add, Subtract, SLT, and Equality Test

| ALU Co  | ontrol Lin | Result   |                    |                                         |  |

|---------|------------|----------|--------------------|-----------------------------------------|--|

| Ainvert | Binvert    | Carry In | Operation          | Kesun                                   |  |

| 0       | 0          | 0        | $0=(00)_{\rm two}$ | AND (a·b)                               |  |

| 0       | 0          | 0        | $1 = (01)_{two}$   | OR (a+b)                                |  |

| 1       | 1          | 0        | $0 = (00)_{two}$   | NOR $(\overline{a} \cdot \overline{b})$ |  |

| 0       | 0          | 0        | $2 = (10)_{two}$   | Add sum(a,b)                            |  |

| 0       | 1          | 1        | $2 = (10)_{two}$   | Subtract (a - b)                        |  |

| 0       | 1          | 1        | $3 = (11)_{two}$   | SLT<br>if (a < b)<br>Result0 = 1        |  |

| 0       | 1          | 1        | $2 = (10)_{two}$   | Test Equality<br>Zero = 1 if $(a < b)$  |  |

#### 8-bit ALU w/ And, OR, Nor, Add,

Subtract, SLT, and Equality Test

#### 32-bit ALU w/ And, OR, Nor, Add,

Subtract, SLT, and Equality Test

# Overview (1)

Goal: Implement a subset of core instructions from the MIPS instruction set, given below

| Category                  | Instruction        | Example            | Meaning                               | Comments |

|---------------------------|--------------------|--------------------|---------------------------------------|----------|

|                           | add                | add \$s1,\$s2,\$s3 | \$s1 ← \$s2+\$s3                      |          |

| A •/ <b>T</b> /•          | subtract           | sub \$s1,\$s2,\$s3 | \$s1 ← \$s2-\$s3                      |          |

| Arithmetic<br>and Logical | and                | add \$s1,\$s2,\$s3 | \$s1 ← \$s2&\$s3                      | & => and |

| 8                         | or                 | or \$s1,\$s2,\$s3  | \$s1 ← \$s2 \$s3                      | => 0r    |

|                           | slt                | slt \$s1,\$s2,\$s3 | If \$s1 < \$s3, \$s1←1<br>else \$s1←0 |          |

| Data Transfer             | load word          | lw \$s1,100(\$s2)  | \$s1 ← Mem[\$s2+100]                  |          |

| Data Hansier              | store word         | sw \$s1,100(\$s2)  | Mem[\$s2+100] ← \$s1                  |          |

| Branch                    | branch on equal    | beq \$s1,\$s2,L    | if(\$s1==\$s2) go to L                |          |

| Dranch                    | unconditional jump | j 2500             | go to 10000                           |          |

## Overview (2)

For each instruction, the first two steps are the same

- Step 1: Based on the address in the program counter (PC), fetch instruction from memory

- Step 2: Read 1 or 2 registers specified in the instruction

Steps 3 and 4 vary from one instruction to another

- Step 3: Perform the arithmetic operation specified by the instruction load/store word (sw/lw): add offset to \$s2 (add/sub/and/or): appropriate operation is performed on \$s2, \$s3 (beq/slt): compare \$s2 and \$s3 (requires \$s2 - \$s3) jump (j): calculate address

- Step 4:

Complete the instruction

sw: write data into memory

lw: read data from memory

add/sub/and/or: store result in \$s1

beq/j: jump to the appropriate instruction

We will now focus on the hardware implementation of each of these instructions

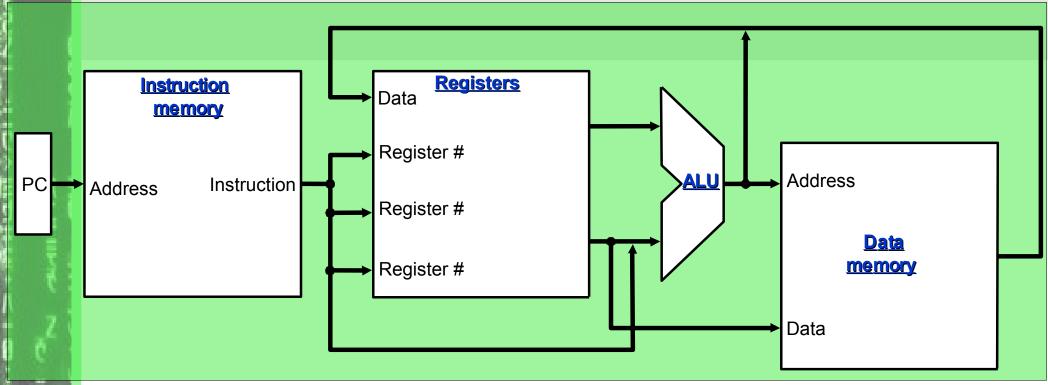

### Abstract view of the Implementation

Program counter provides the instruction address 1.

"[

- 2. Instruction is fetched from instruction memory based on address in the PC

- 3. Register numbers are specified by the instruction

- ALU computes an arithmetic result or address of memory 4.

- Arithmetic operation: Result is saved in a register

- Data transfer: Data is extracted from data memory & transferred to a register or vice versa -W-7-M 75

### Basics: Sequential vs. Combinational Circuits (1)

Digital circuits can be classified into two categories

- 1. Combinational Circuits:

- Output depends only on the current input

- Same set of inputs will always produce the same output

- Consist of AND, OR, NOR, NAND, and NOT gates

- Common examples are adder circuits and ALU

- 2. Sequential Circuits:

- Output depends on the current input and state of the circuit

- Same set of inputs can produce completely different outputs

- Consist of memory elements such as flip-flops and registers in addition to combinational circuits

- Examples are traffic signals and street lights

Datapath and control circuits of an ALU use sequential circuits.

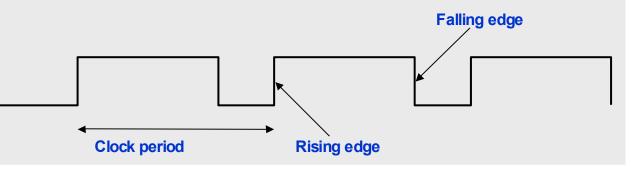

### Basics: Clocks (2)

- 1. Clock provides a periodic signal oscillating between low and high states with fixed cycle time.

- 2. Clock frequency is inverse of clock cycle time. What is the cycle time for 1GHz clock?

- 3. Clock controls when the state of a memory element changes.

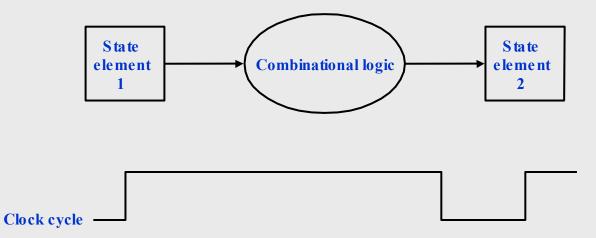

- 4. We assume falling edge-triggered clocking implying that the state changes only at the falling edge. When is the state element 2 modified in the following circuit?

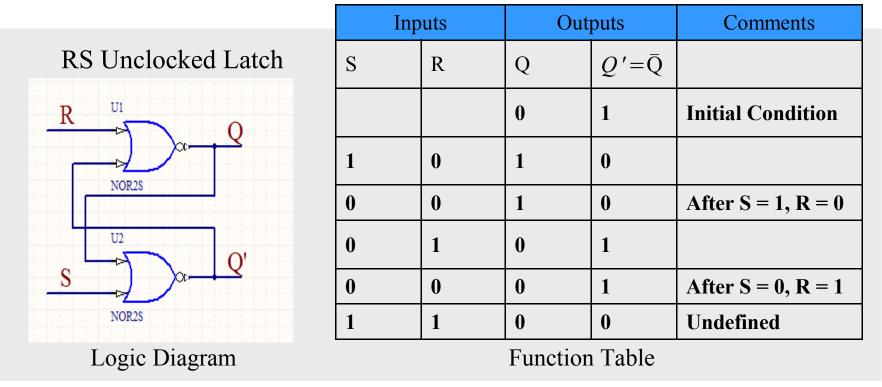

# Basics: RS Latch (3)

Simplest memory elements are Flip-flops and Latches

- In clocked latches, state changes whenever input changes and the clock is asserted.

- In flip-flops, state changes only at the trailing edge of the clock

- For a RS-latch: output Q = 1 when S = 1, R = 0 (set condition) output Q = 0 when S = 0, R = 1 (reset condition)

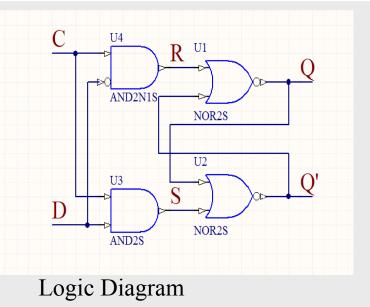

## Basics: Clocked D Latch (4)

1. For a D-latch: output Q = 1 when D = 1 (set condition) output Q = 0 when D = 0 (reset condition)

-"I

| Inp | outs | Out | puts           | Comments |  |

|-----|------|-----|----------------|----------|--|

| C   | C D  |     | $Q' = \bar{Q}$ |          |  |

| 0   | 0 X  |     | anged          |          |  |

| 1   | 1 0  |     | 1              | Reset    |  |

| 1   | 1 1  |     | 0              | Set      |  |

Function Table

2. D Latch requires clock to be asserted for output to change

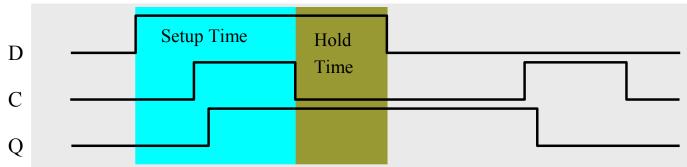

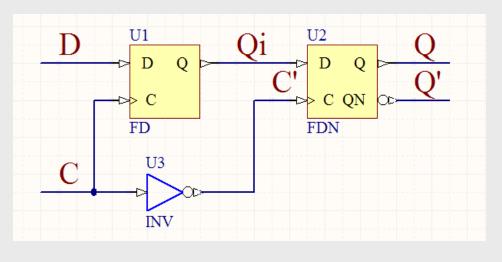

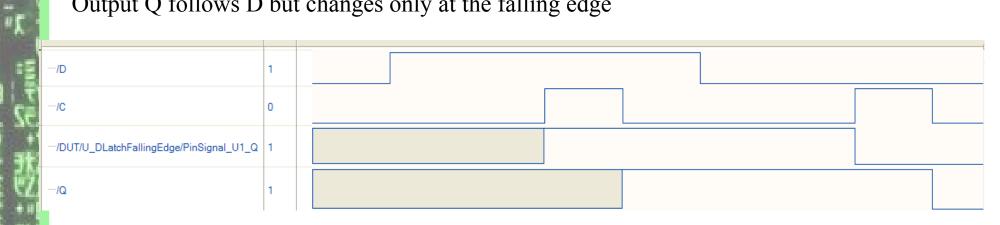

### Basics: Falling Edge Triggered D flip-flop (5)

Logic Diagram

Output Q follows D but changes only at the falling edge

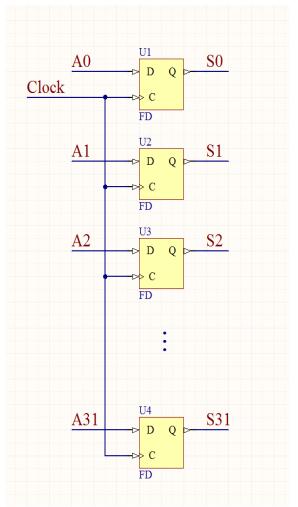

### Basics: 32-bit Registers (6)

Falling edge triggered D flip-flops can be combined to form a register