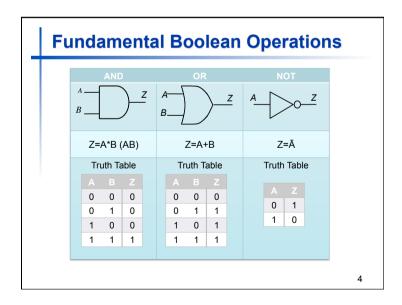

#### **Boolean Algebra**

- A *truth table* specifies output signal logic values for every possible combination of input signal logic values

- In evaluating Boolean expressions, the Operation Hierarchy is: 1) NOT 2) AND 3) OR. Order can be superseded using ( ... )

- **Example**: *A* = *T*,*B* = *F*,*C* = *T*,*D* = *T*

- What is the value of  $Z = (\overline{A} + B) \cdot (C + \overline{B} \cdot D)$ ?

5

$Z = (\overline{T} + F) \cdot (C + \overline{B} \cdot D) = (F + F) \cdot (C + \overline{B} \cdot D)$  $= F \cdot (C + \overline{B} \cdot D) = F$

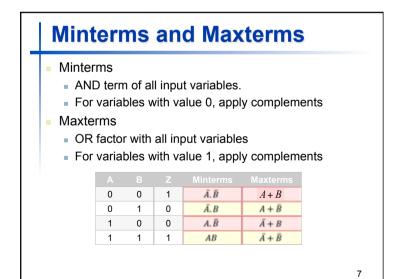

| <ul> <li>A function with <i>n</i> variables has 2<sup>n</sup> minterms (and Maxterms) – exactly equal to the number of rows in truth table</li> <li>Each minterm is true for exactly one combination of inputs</li> <li>Each Maxterm is false for exactly one combination of inputs</li> <li>Each Maxterm is false for exactly one combination of inputs</li> </ul> | Minte   | rm               | s a              | and              | <b>Maxt</b>                   | terms                               |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|------------------|------------------|-------------------------------|-------------------------------------|-----------|

| inputs<br>Each Maxterm is false for exactly one combination of inputs<br>A B Z Minterms Maxterms<br>0 0 1 Ā.B A+B<br>0 1 0 Ā.B A+B<br>1 0 0 A.B Ā+B                                                                                                                                                                                                                 | Maxterr | ns) –            |                  |                  |                               |                                     |           |

| <ul> <li>Each Maxterm is false for exactly one combination of inputs</li> <li>A B Z Minterms Maxterms</li> <li>0 0 1</li> <li>A B A + B</li> <li>0 1</li> <li>A B A + B</li> <li>1 0</li> <li>A B A + B</li> </ul>                                                                                                                                                  |         | interr           | n is ti          | rue fo           | r exactly o                   | ne combina                          | ation of  |

| inputs<br>A B Z Minterms Maxterms<br>0 0 1 $\overline{A}.\overline{B}$ $A+B$<br>0 1 0 $\overline{A}.B$ $A+\overline{B}$<br>1 0 0 $A.\overline{B}$ $\overline{A}+B$                                                                                                                                                                                                  | inputs  |                  |                  |                  |                               |                                     |           |

| 0         0         1 $\overline{A}.\overline{B}$ $A+B$ 0         1         0 $\overline{A}.B$ $A+\overline{B}$ 1         0         0 $A.\overline{B}$ $\overline{A}+B$                                                                                                                                                                                             |         |                  |                  |                  |                               |                                     |           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                               |         | axter            | m is f           | false f          | for exactly                   | one combir                          | nation of |

| 1 0 0 $A.\overline{B}$ $\overline{A}+B$                                                                                                                                                                                                                                                                                                                             |         |                  |                  |                  | -                             |                                     | nation of |

|                                                                                                                                                                                                                                                                                                                                                                     |         | А                | В                | Z                | Minterms                      | Maxterms                            | nation of |

| 1 1 1 $AB$ $\overline{A} + \overline{B}$                                                                                                                                                                                                                                                                                                                            |         | A<br>0           | B<br>0           | Z<br>1           | Minterms<br><u>Ā.B</u>        | Maxterms<br>A+B                     | nation of |

|                                                                                                                                                                                                                                                                                                                                                                     |         | A<br>0<br>0      | B<br>0<br>1      | Z<br>1<br>0      | Minterms<br>Ā.B<br>Ā.B        | Maxterms<br>A + B<br>A + B          | nation of |

|                                                                                                                                                                                                                                                                                                                                                                     |         | A<br>0<br>0<br>1 | B<br>0<br>1<br>0 | Z<br>1<br>0<br>0 | Minterms<br>Ā.B<br>Ā.B<br>A.B | Maxterms<br>A + B<br>A + B<br>Ā + B | nation of |

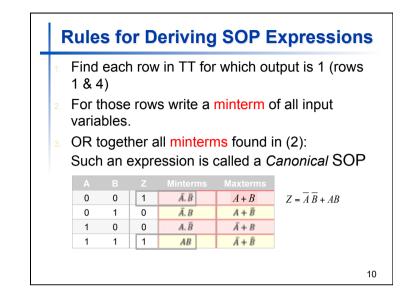

| (1<br>2. F<br>3. A | ows<br>or th | 2 &<br>lose | 3)<br>rows | s write a I | which ou<br>maxterm<br>rm found |                                            |

|--------------------|--------------|-------------|------------|-------------|---------------------------------|--------------------------------------------|

| 5                  | Such         | an e        |            |             | called a C                      | · · /                                      |

| P                  | OS.          |             |            |             |                                 |                                            |

|                    |              | В           | Z          | Minterms    | Maxterms                        |                                            |

|                    | 0            | 0           | 1          | Ā. B        | A + B                           |                                            |

|                    | 0            | 1           | 0          | Ā. B        | $A + \overline{B}$              | $Z = (A + \overline{B})(\overline{A} + B)$ |

|                    | 1            | 0           | 0          | A. B        | $\overline{A} + B$              | L = (I + D)(I + D)                         |

|                    | 1            | 1           | 1          | AB          | $\bar{A} + \bar{B}$             |                                            |

| La                 |              |             |            | -           |                                 | - 11                                       |

## Activity 1

Derive SOP and POS expressions for the following TT.

| Α | в | Carry |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 0     |

| 1 | 0 | 0     |

| 1 | 1 | 1     |

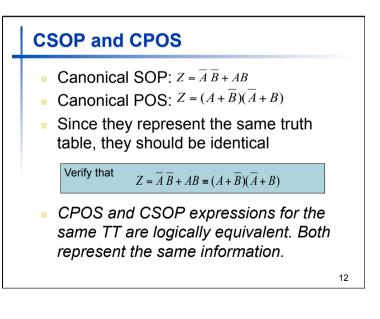

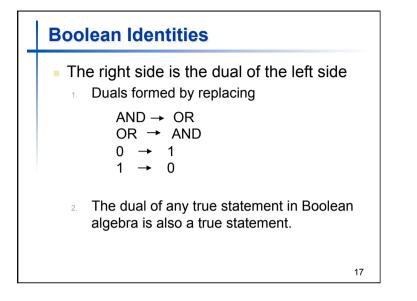

|                                                              | <b>Boolean Identities</b>                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                              | Useful for simplifying I                                                                                                                                                                                                                                                                                                                                                      | ogic equations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                              | (a)                                                                                                                                                                                                                                                                                                                                                                           | (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1                                                            | $\overline{A} = A$                                                                                                                                                                                                                                                                                                                                                            | $\overline{\overline{A}} = A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | $A + true = true (A + 1 = 1)$ $A + \underline{A} = A$ $A + \overline{A} = true (A + \overline{A} = 1)$ $A + B = B + A$ $A + B + C = (A + B) + C = A + (B + C)$ $A \cdot (B + C) = \underline{A} \cdot \underline{B} + A \cdot C$ $A + B = \overline{A} \cdot \overline{B}$ $A \cdot B + A \cdot \overline{B} = A$ $A + A \cdot B = A$ $A + A \cdot B = A$ $A + A \cdot B = A$ | $\begin{array}{rl} A\cdot \operatorname{true} = A & (A\cdot 1 = A) \\ A \cdot \operatorname{false} = \operatorname{false} & (A \cdot 0 = 0) \\ A \cdot A = A \\ A \cdot \overline{A} = \operatorname{false} & (A \cdot \overline{A} = 0) \\ A \cdot B = B \cdot A \\ A \cdot \overline{B} = C = (A \cdot B) \cdot C = A \cdot (B \cdot C) \\ A + B \cdot C = (A + B)(A + C) \\ \overline{A \cdot B} = \overline{A} + \overline{B} \\ (A + B)(A + \overline{B}) = A \\ A(A + B) = A \\ A + \overline{A} \cdot B = A + B \\ (A + B)(\overline{A} + C)(B + C) = (A + B)(\overline{A} + C) \end{array}$ |

|                                                              | Duals                                                                                                                                                                                                                                                                                                                                                                         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| В | oolear     | n Identities                                         |    |

|---|------------|------------------------------------------------------|----|

|   | Identities | Property                                             |    |

|   | 1-5        | Single variable, foundations of Boolean manipulation |    |

|   | 6          | Commutative                                          |    |

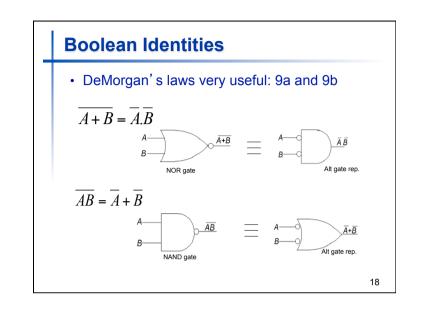

|   | 7          | Associative                                          |    |

|   | 8          | Distributive                                         |    |

|   | 9          | De Morgan's                                          |    |

|   | 10         | Combining                                            |    |

|   | 11         | Absorption                                           |    |

|   | 13         | Consensus                                            |    |

|   |            |                                                      |    |

|   |            |                                                      |    |

|   |            |                                                      | 16 |

|   |            |                                                      | 16 |

| Activi | ty 2                                           |    |

|--------|------------------------------------------------|----|

| Proofs | of some Identities:                            |    |

| 12b:   | $A + \overline{AB} = A + B$                    |    |

| 13a:   | $AB + \overline{AC} + BC = AB + \overline{AC}$ |    |

|        |                                                |    |

|        |                                                |    |

|        |                                                |    |

|        |                                                | 19 |

| CSE 2021 Computer Organization |

|--------------------------------|

|                                |

| Sequential Circuits            |

|                                |

|                                |

|                                |

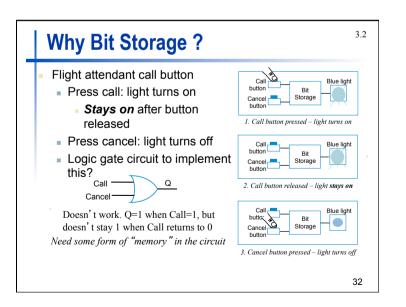

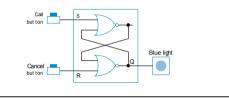

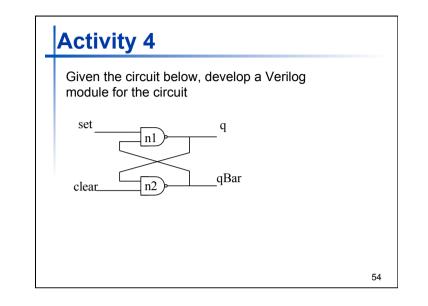

# Bit Storage Using SR Latch

- Simplest memory elements are Latch and Flip-Flops

- SR (set-reset) latch is an *un-clocked* latch

- Output Q=1 when S=1, R=0 (set condition)

- Output Q=0 when S=0, R=1 (reset condition)

33

Problem - Q is undefined if S=1 and R=1

| CSE 2021 Computer Organization |

|--------------------------------|

|                                |

| Verilog Basics                 |

|                                |

|                                |

|                                |

| What is                                                                 | an HDL?                                                                                                |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| a software                                                              | re Description Language (HDL) is<br>e programming language used to<br>intended operation of a piece of |

| <ul> <li>The difference</li> <li>Concurrence</li> <li>Timing</li> </ul> | ence between an HDL and "C"<br>ency                                                                    |

| that we ca                                                              | Il feature of the Verilog HDL is<br>an use the same language for<br>g, testing and debugging the       |

| system.                                                                 | 40                                                                                                     |

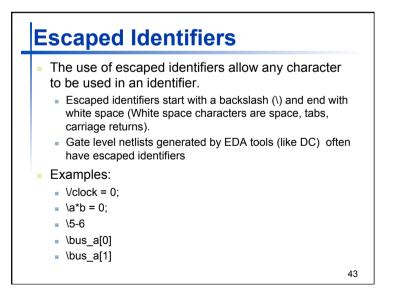

### **Identifiers**

- Identifiers are names assigned by the user to Verilog objects such as modules, variables, tasks etc.

- An identifier may contain any sequence of letters, digits, a dollar sign '\$', and the underscore '\_' symbol.

- The first character of an identifier must be a letter or underscore; it cannot be a dollar sign '\$', for example. We cannot use characters such as '-' (hyphen), brackets, or '#' in Verilog names (escaped identifiers are an exception).

| • | _ |  |

|---|---|--|

|   |   |  |

|   |   |  |

|   |   |  |

| <b>module</b> identifiers; /* Multiline comments in Verilog look lil<br>and // is OK in here. */<br>// Single-line comment in Verilog. | ke C comments |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------|

| reg legal_identifier, two_underscores;                                                                                                 |               |

| reg_OK,OK_,OK_\$,OK_123,CASE_SENSITIVE, case_                                                                                          | sensitive;    |

| reg Vclock ,\a*b ; // Add white_space after escaped ident                                                                              | ifier.        |

| //reg \$_BAD,123_BAD; // Bad names even if we declare                                                                                  | them!         |

| initial begin                                                                                                                          |               |

| legal_identifier = 0; // Embedded underscores are OK                                                                                   | ,<br>,        |

| twounderscores = 0; // even two underscores in a r                                                                                     | OW.           |

| _OK = 0; // Identifiers can start with underscore                                                                                      |               |

| OK_ = 0; // and end with underscore.                                                                                                   |               |

| OK\$ = 0; // \$ sign is OK.                                                                                                            |               |

| OK_123 =0; // Embedded digits are OK.                                                                                                  |               |

| CASE_SENSITIVE = 0; // Verilog is case-sensitive (u                                                                                    | nlike VHDL).  |

| case_sensitive = 1;                                                                                                                    |               |

| Vclock = 0; // An escaped identifier with \ breaks rules                                                                               | 5             |

| $a^{t} = 0$ ; // but be careful to watch the spaces!                                                                                   |               |

| \$display("Variable CASE_SENSITIVE= %d",CASE_S                                                                                         |               |

| \$display("Variable case_sensitive= %d",case_sensitiv                                                                                  | ve);          |

| \$display("Variable Vclock = %d",Vclock );                                                                                             |               |

| <pre>\$display("Variable \\a*b = %d",\a*b ); end</pre>                                                                                 | An Example    |

| endmodule                                                                                                                              | An Example 44 |

| enuniouule                                                                                                                             |               |

#### Simulation Result of the Example

Variable CASE\_SENSITIVE= 0 Variable case\_sensitive= 1 Variable /clock = 0 Variable \a\*b = 0

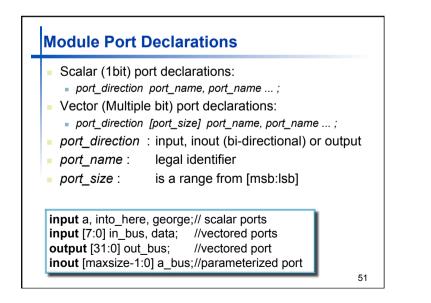

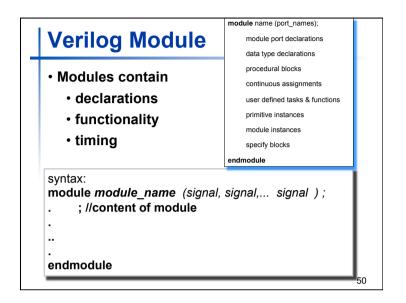

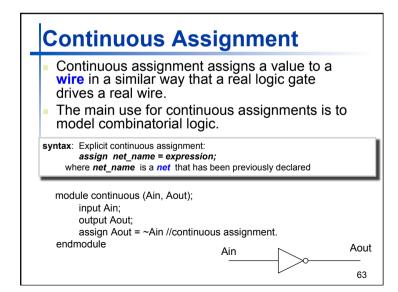

## **Design Entities**

- The module is the basic unit of code in the Verilog language.

- Example

module holiday\_1(sat, sun,weekend);

input sat, sun;

output weekend;

assign weekend = sat | sun;

endmodule

| Module Instances                                                                                                                   |   |

|------------------------------------------------------------------------------------------------------------------------------------|---|

| <ul> <li>A module may be instantiated within another module</li> <li>There may be multiple instances of the same module</li> </ul> |   |

| syntax for instantiation:<br><i>module_name instance_name</i> (signal, signal,);                                                   |   |

|                                                                                                                                    | 1 |

| module example (a,b,c,d);<br>input a,b;<br>output c,d;                                                                             |   |

| output o,u,                                                                                                                        |   |

| endmodule                                                                                                                          |   |

|                                                                                                                                    |   |

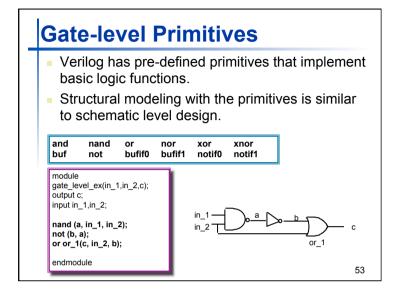

| <b>User-Defined Primitives</b>                                                                                                                                                                                                               |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| We can define primitive gates (a user-defined<br>primitive or UDP) using a truth-table specification.<br>The first port of a UDP must be an output port, and<br>this must be the only output port (we may not use<br>vector or inout ports). |    |

| <ul> <li>An example</li> <li>primitive Adder(Sum, InA, InB);</li> <li>output Sum;</li> </ul>                                                                                                                                                 |    |

| input InA, InB;<br>table // inputs : output                                                                                                                                                                                                  |    |

| 00 : 0;<br>01 : 1;                                                                                                                                                                                                                           |    |

| 10 : 1;<br>11 : 0;                                                                                                                                                                                                                           |    |

| endtable<br>endprimitive                                                                                                                                                                                                                     |    |

|                                                                                                                                                                                                                                              | 55 |

| Operators                                                            |

|----------------------------------------------------------------------|

| Verilog operators (in increasing order of precedence)                |

| ?: (conditional)                                                     |

| <ul> <li>II (logical or)</li> </ul>                                  |

| && (logical and)                                                     |

| <ul> <li>I (bitwise or)</li> </ul>                                   |

| <ul> <li>~  (bitwise nor)</li> </ul>                                 |

| (bitwise xor)                                                        |

| ^~ ~^ (bitwise xnor, equivalence)                                    |

| <ul> <li>&amp; (bitwise and)</li> <li>&amp; (bitwise and)</li> </ul> |

| ~& (bitwise nand)                                                    |

| = = (logical) != (logical) === (case) !== (case)                     |

| <ul> <li>&lt;(it)</li> <li>&lt;= (it or equal)</li> </ul>            |

| <ul> <li>&gt; (qt)</li> </ul>                                        |

| $\Rightarrow$ (gt) $\Rightarrow$ (gt or equal)                       |

| <ul> <li>&lt;&lt; (shift left)</li> </ul>                            |

| shift right)                                                         |

| + (addition)                                                         |

| <ul> <li>- (subtraction)</li> </ul>                                  |

| * (multiply)                                                         |

| / (divide)                                                           |

| • % (modulus) 56                                                     |

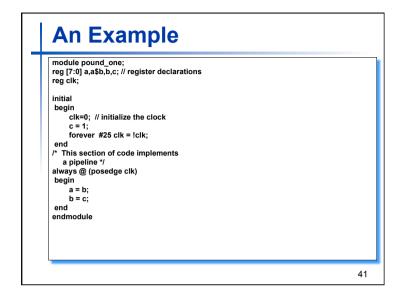

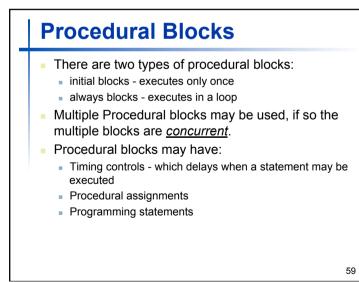

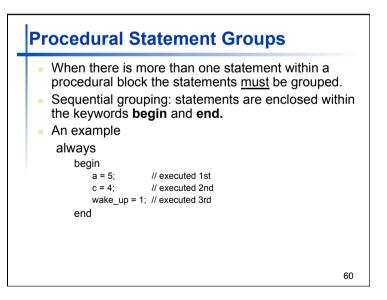

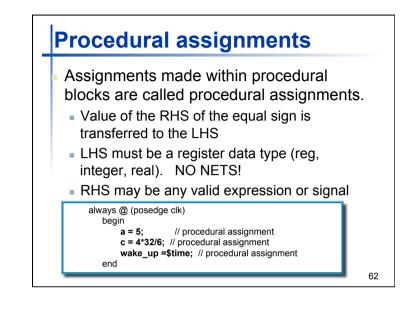

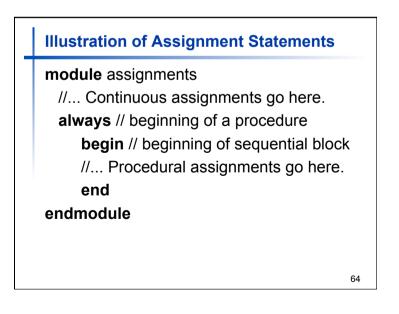

### **Procedures**

- A Verilog procedure is an always or initial statement, a task, or a function.

- The statements within a sequential block (statements that appear between a begin and an end) that is part of a procedure execute sequentially in the order in which they appear, but the procedure executes concurrently with other procedures.

#### Timing Controls (procedural delays)

- #delay

simple delay

Delays execution for a specific number of time steps.

#5 reg a = reg b;

- @ (edge signal) edge-triggered timing control

Delays execution until a transition on signal occurs.

edge is optional and can be specified as either posedge or negedge.

Several signal arguments can be specified using the

- An example : always @ (posedge clk) reg a = reg b;

- wait (expression) level-sensitive timing control

Delays execution until expression evaluates true.

wait (cond is true) reg a = reg b;

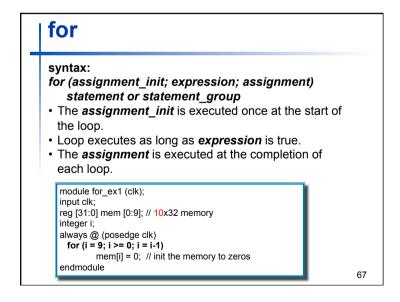

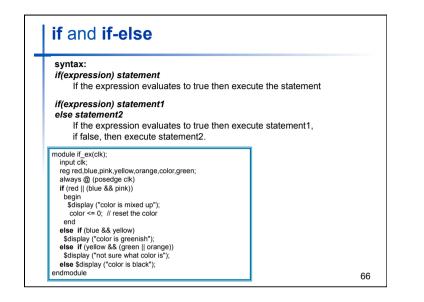

### **Control Statements**

- Two types of programming statements:

- Conditional

- Looping

- Programming statements only used in procedural blocks

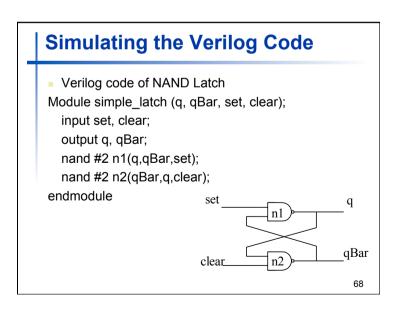

## Testbench

- A testbench generates a sequence of input values (we call these input vectors) that test or exercise the verilog code.

- It provides stimulus to the statement that will monitor the changes in their outputs.

- Testbenchs do not have a port declaration but must have an instantiation of the circuit to be tested.

69

# A testbench for NAND Latch

Module test simple latch; wire q, gBar; reg set, clear; simple\_latch SL1(q,qBar,set,clear); initial begin #10 set = 0; clear = 1; #10 set = 1; #10 clear = 0; #10 clear = 1; #10 \$stop; #10 \$finish; end initial begin \$monitor ("%d set= %b clear= %b q=%b qBar=%b",\$time, set.clear.q.qBar); end endmodule