## **CSE 2021 Computer Organization**

#### **Appendix C Part 2**

**Basic Arithmetic Logic Unit** -- Adder

#### **Half Adders**

- Need to add bits {0,1} of A<sub>i</sub> and B<sub>i</sub>

- Associate

$$A: A_{\mu} \dots A_{\mu_1} A_{\mu_1} A_{\mu_2} \dots A_{\mu_n}$$

- binary bit  $0 \leftrightarrow \text{logic value F } (0)$   $B: B_1 \dots B_{p+1} B_1 \dots B_p$

- binary bit 1  $\leftrightarrow$  logic value T (1)

- This leads to the following truth table

| <b>A</b> <sub>i</sub> | B <sub>i</sub> | Sum <sub>i</sub> | Carry <sub>i+1</sub> |

|-----------------------|----------------|------------------|----------------------|

| 0                     | 0              | 0                | 0                    |

| 0                     | 1              | 1                | 0                    |

| 1                     | 0              | 1                | 0                    |

| 1                     | 1              | 0                | 1                    |

$$SUM_i = \overline{A_i}B_i + A_i\overline{B_i} = A_i \oplus B_i$$

$$CARRY_{i+1} = A_i B_i$$

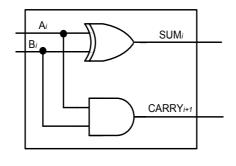

#### **Half Adder Circuit**

$$SUM_{i} = \overline{A_{i}}B_{i} + A_{i}\overline{B_{i}} = A_{i} \oplus B_{i}$$

$$CARRY_{i+1} = A_{i}B_{i}$$

### **Half Adder Limitations**

Half adder circuits do not suffice for general addition because they do not include the carry bit from the previous stage of addition, e.g.

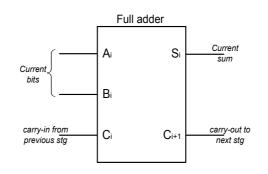

# Full Adders (1-Bit ALU)

Full adders can use the carry bit from the previous stage of addition

| $A_i$ | B <sub>i</sub> | $C_i$ | Si | C <sub>i+1</sub> |

|-------|----------------|-------|----|------------------|

| 0     | 0              | 0     | 0  | 0                |

| 0     | 0              | 1     | 1  | 0                |

| 0     | 1              | 0     | 1  | 0                |

| 0     | 1              | 1     | 0  | 1                |

| 1     | 0              | 0     | 1  | 0                |

| 1     | 0              | 1     | 0  | 1                |

| 1     | 1              | 0     | 0  | 1                |

| 1     | 1              | 1     | 1  | 1                |

## **Full Adder Logic Expressions**

Sum

$$SUM = \overline{A}_i \overline{B}_i C_i + \overline{A}_i B_i \overline{C}_i + A_i \overline{B}_i \overline{C}_i + A_i B_i C_i$$

$$= \overline{A}_i (\overline{B}_i C_i + B_i \overline{C}_i) + A_i (\overline{B}_i \overline{C}_i + B_i C_i)$$

$$= \overline{\mathsf{A}}_{\mathsf{i}} \big( \mathsf{B}_{\mathsf{i}} \oplus \mathsf{C}_{\mathsf{i}} \big) + \mathsf{A}_{\mathsf{i}} \big( \overline{\mathsf{B}_{\mathsf{i}} \oplus \mathsf{C}_{\mathsf{i}}} \big)$$

$$= A_i \oplus B_i \oplus C_i$$

Carry

$$C_{i+1} = A_i B_i + A_i \overline{B}_i C_i + \overline{A}_i B_i C_i$$

$$= A_i B_i + C_i (A_i \overline{B}_i + \overline{A}_i B_i)$$

$$= A_i B_i + C_i (A_i \oplus B_i)$$

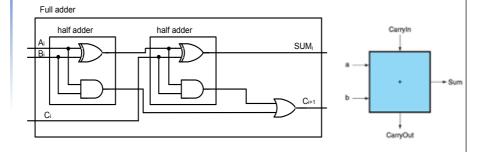

## **Full Adder Circuit**

$$SUM = (A_i \oplus B_i) \oplus C_i$$

$$C_{i+1} = A_i B_i + C_i (A_i \oplus B_i)$$

Note: A full adder adds 3 bits. Can also consider as first adding first two and then the result with the carry

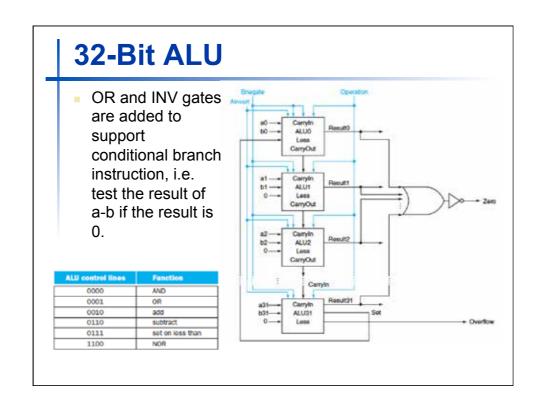

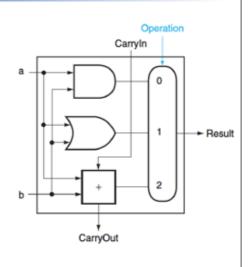

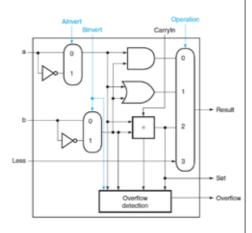

## **Enhancement to 1-bit Adder(1)**

- 1-bit ALU with AND, OR, and addition

- Supplemented with AND and OR gates

- A multiplexer controls which gate is connected to the output

| Operation | Result   |

|-----------|----------|

| 00        | AND      |

| 01        | OR       |

| 10        | Addition |

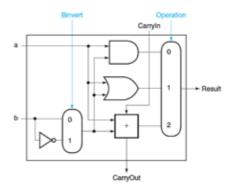

## **Enhancement to 1-bit Adder(2)**

- 1-bit ALU for subtraction

- Subtraction is performed using 2's complement, i.e.

$$a-b=a+\overline{b}+1$$

| Binvert | CarryIn | Operation | Result      |

|---------|---------|-----------|-------------|

| 0       | 0       | 00        | AND         |

| 0       | 0       | 01        | OR          |

| 0       | 0       | 10        | Addition    |

| 1       | 1       | 10        | Subtraction |

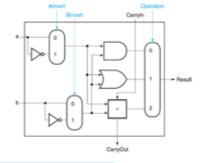

# **Enhancement to 1-bit Adder(3)**

- 1-bit ALU for NOR operation

- A MIPS ALU also needs a NOR function

$$\overline{(a+b)} = \overline{a} \cdot \overline{b}$$

| Ainvert | Binvert | CarryIn | Operation | Result      |

|---------|---------|---------|-----------|-------------|

| 0       | 0       | 0       | 00        | AND         |

| 1       | 1       | 0       | 00        | NOR         |

| 0       | 0       | 0       | 01        | OR          |

| 0       | 0       | 0       | 10        | Addition    |

| 1       | 1       | 1       | 10        | Subtraction |

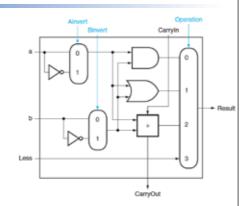

#### **Enhancement to 1-bit Adder(4)**

- 1-bit ALU for SLT operations

- slt \$s1, \$s2, \$s3

- If (\$s2<\$s3), \$s1=1, else \$s1=0

- adding one input less

- if (a<b), set *less* to 1or if (a-b)<0, set *less* to 1

- If the result of subtraction is negative, set less to 1

- How to determine if the result is negative?

# **Enhancement to 1-bit Adder(5)**

- How to determine if the result is negative?

- Negative → Sign bit value=1

- Create a new output "Set" and used only for slt

- An overflow detection is included

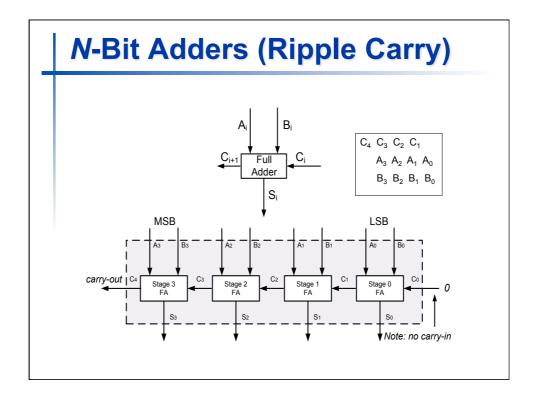

#### **Ripple Carry Adders**

- 4 FA's cascaded to form a 4-bit adder

- In general, N FA's can be used to form a N-bit adder

- Carry bits have to propagate from one stage to the next. Inherent propagation delays associated with this

- Output of each FA is therefore not stable until the carry-in from the previous stage is calculated