| System  | Why?                                                    | Remarks                                |

|---------|---------------------------------------------------------|----------------------------------------|

| Decimal | Base 10 (10 fingers)                                    | Most used system                       |

| Binary  | Base 2. On/Off<br>systems                               | 3 times more<br>digits than<br>decimal |

| Octal   | Base 8.Shorthand<br>notation for working<br>with binary | 3 times less<br>digits than binary     |

| Hex     | Base 16                                                 | 4 times less<br>digits than binary     |

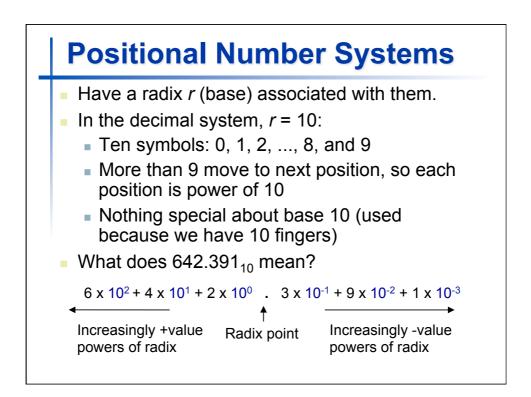

| What do                                 | es 64        | 2.39                    |                        | ean?                      |                            |                             |

|-----------------------------------------|--------------|-------------------------|------------------------|---------------------------|----------------------------|-----------------------------|

| Base 10<br>( <i>r</i> )                 | 10²<br>(100) | 10 <sup>1</sup><br>(10) | 10 <sup>0</sup><br>(1) | 10 <sup>-1</sup><br>(0.1) | 10 <sup>-2</sup><br>(0.01) | 10 <sup>-3</sup><br>(0.001) |

| Coefficient<br>(a <sub>i</sub> )        | 6            | 4                       | 2                      | 3                         | 9                          | 1                           |

| Product: a <sub>i</sub> *r <sup>i</sup> | 600          | 40                      | 2                      | 0.3                       | 0.09                       | 0.001                       |

| Value                                   | = 600        | + 40 + 2                | + 0.3 + (              | 0.09 + 0.                 | 001 = 64                   | 12.391                      |

| Multiply ea<br>and add th<br>In general | nem tog      | -                       |                        | riate p                   | ower                       | of 10                       |

| Number<br>system | Radix | Symbols                           |

|------------------|-------|-----------------------------------|

| Binary           | 2     | {0,1}                             |

| Octal            | 8     | {0,1,2,3,4,5,6,7}                 |

| Decimal          | 10    | {0,1,2,3,4,5,6,7,8,9}             |

| Hexadecimal      | 16    | {0,1,2,3,4,5,6,7,8,9,a,b,c,d,e,f} |

|                  |       |                                   |

| Decimal | Binary | Decimal | Binary |

|---------|--------|---------|--------|

| 0       | 0000   | 8       | 1000   |

| 1       | 0001   | 9       | 1001   |

| 2       | 0010   | 10      | 1010   |

| 3       | 0011   | 11      | 1011   |

| 4       | 0100   | 12      | 1100   |

| 5       | 0101   | 13      | 1101   |

| 6       | 0110   | 14      | 1110   |

| 7       | 0111   | 15      | 1111   |

| Decimal | Octal | Decimal | Octal |

|---------|-------|---------|-------|

| 0       | 0     | 8       | 10    |

| 1       | 1     | 9       | 11    |

| 2       | 2     | 10      | 12    |

| 3       | 3     | 11      | 13    |

| 4       | 4     | 12      | 14    |

| 5       | 5     | 13      | 15    |

| 6       | 6     | 14      | 16    |

| 7       | 7     | 15      | 17    |

| exaded  | imal | Numb    | er Sys |

|---------|------|---------|--------|

| Decimal | Hex  | Decimal | Hex    |

| 0       | 0    | 8       | 8      |

| 1       | 1    | 9       | 9      |

| 2       | 2    | 10      | Α      |

| 3       | 3    | 11      | В      |

| 4       | 4    | 12      | С      |

| 5       | 5    | 13      | D      |

| 6       | 6    | 14      | E      |

| 7       | 7    | 15      | F      |

|         |      |         |        |

|         |      |         |        |

|         |      |         |        |

|         |      |         |        |

| Decimal | Binary | Octal | Hex | Decimal | Binary | Octal | Hex |

|---------|--------|-------|-----|---------|--------|-------|-----|

| 0       | 0000   | 0     | 0   | 8       | 1000   | 10    | 8   |

| 1       | 0001   | 1     | 1   | 9       | 1001   | 11    | 9   |

| 2       | 0010   | 2     | 2   | 10      | 1010   | 12    | Α   |

| 3       | 0011   | 3     | 3   | 11      | 1011   | 13    | В   |

| 4       | 0100   | 4     | 4   | 12      | 1100   | 14    | С   |

| 5       | 0101   | 5     | 5   | 13      | 1101   | 15    | D   |

| 6       | 0110   | 6     | 6   | 14      | 1110   | 16    | E   |

| 7       | 0111   | 7     | 7   | 15      | 1111   | 17    | F   |

|         |        |       |     |         |        |       |     |

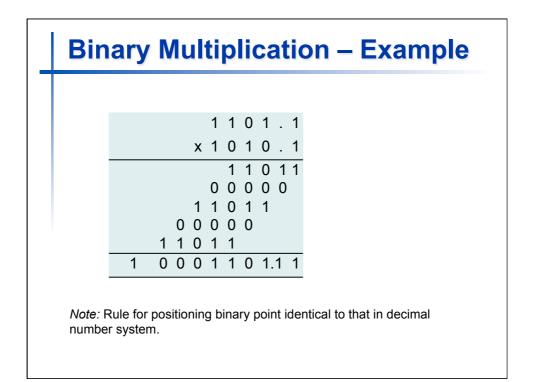

| Bina | ry I | Mu  | ultipli | catior | ı |  |

|------|------|-----|---------|--------|---|--|

| axb  |      |     |         |        |   |  |

|      |      |     |         |        |   |  |

|      | Tr   | uth | table   |        |   |  |

|      | а    | b   | Product |        |   |  |

|      | 0    | 0   | 0       |        |   |  |

|      | 0    | 1   | 0       |        |   |  |

|      | 1    | 0   | 0       |        |   |  |

|      | 1    | 1   | 1       |        |   |  |

| No. of<br>bits Distinct nos.   1 2 {0,1}   2 4 {00, 01, 10, 11}   3 8 {000, 001, 010, 011, 100, 101, 110, 11 | No of |                                           |

|--------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------|

| 2 4 {00, 01, 10, 11}                                                                                         |       | Distinct nos.                             |

|                                                                                                              | 1     | 2 {0,1}                                   |

| 3 8 (000, 001, 010, 011, 100, 101, 110, 11                                                                   | 2     | 4 {00, 01, 10, 11}                        |

|                                                                                                              | 3     | 8 {000, 001, 010, 011, 100, 101, 110, 111 |

| n 2 <sup>n</sup>                                                                                             | n     | 2 <sup>n</sup>                            |

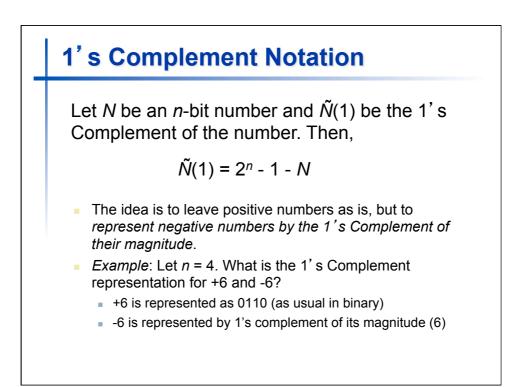

| 4-bit No. | SM | 1's C | 2's C |                                          |

|-----------|----|-------|-------|------------------------------------------|

| 0000      | +0 | +0    | 0     | In all 3 representations, a              |

| 0001      | 1  | 1     | 1     | –ve number has a 1 in                    |

| 0010      | 2  | 2     | 2     | _                                        |

| 0011      | 3  | 3     | 3     | MSB location                             |

| 0100      | 4  | 4     | 4     | To handle –ve numbers                    |

| 0101      | 5  | 5     | 5     |                                          |

| 0110      | 6  | 6     | 6     | using <i>n</i> bits,                     |

| 0111      | 7  | 7     | 7     | ■ ≅ 2 <sup>n-1</sup> symbols can be used |

| 1000      | -0 | -7    | -8    | for positive numbers                     |

| 1001      | -1 | -6    | -7    | •                                        |

| 1010      | -2 | -     | -6    | $= 2^{n-1} \text{ symbols can be used}$  |

| 1011      | -3 |       | -5    | for negative umbers                      |

| 1100      |    | -3    | -4    | In 2' s C notation, only 1               |

| 1101      | -5 | _     | -3    |                                          |

| 1110      | -6 | -1    | -2    | combination used for 0                   |

| 1111      | -7 | -0    | -1    |                                          |

|    |       |                  |    | 2's C arith |                |

|----|-------|------------------|----|-------------|----------------|

| 1. | (+5)  | 0101             | 2. | (-5)        | 1011           |

|    | +(+2) | +0010            |    | +(+2)       | +0010          |

|    | (+7)  | 0111             |    | (-3)        | 1101           |

| 3. | (+5)  | 0101             | 4. | (-5)        | 1011           |

|    | +(-2) | +1110            |    | +(-2)       | +1110          |

|    | (+3)  | 1 0011           |    | (-7)        | 1 1001         |

|    | · ,   | ignore the carry |    | ( )         | ignore the car |

| CSE4210 Architecture & Hardware for DSP |

|-----------------------------------------|

|                                         |

| Verilog                                 |

| leneg                                   |

|                                         |

|                                         |

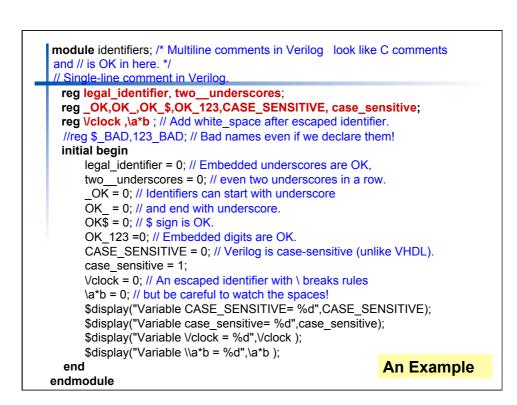

## **Simulation Result of the Example**

Variable CASE\_SENSITIVE= 0 Variable case\_sensitive= 1 Variable /clock = 0 Variable \a\*b = 0

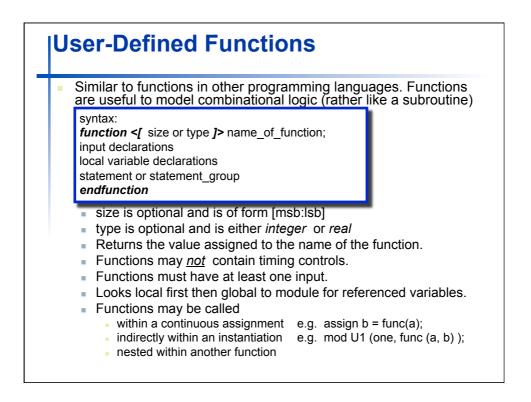

| Function - Example                                         |                                  |

|------------------------------------------------------------|----------------------------------|

| define FALSE 0<br>define TRUE 1                            |                                  |

| nodule function ex (clk);                                  |                                  |

| iput clk;                                                  |                                  |

| eg r1,r2,r3;                                               |                                  |

| unction error; // the function de                          | finition                         |

| nput[7:0] a,b,c;                                           |                                  |

| if ((a !=b) && (a !=c))<br>error = `FALSE; // assign value | to the name of the function      |

| else error = `TRUE;<br>ndfunction                          |                                  |

| nununcuon                                                  |                                  |

| lways @ (posedge clk)                                      |                                  |

| f (error(r1,r2,r3)) // call of the fu                      | nction                           |

| display ("error in reg compare");                          |                                  |

| another example call below                                 |                                  |

| eg d;                                                      |                                  |

| lways @ (posedge clk)                                      | A function can be called where a |

| d = error(r1,r2,r3);                                       | value may be placed in your code |

| ndmodule                                                   |                                  |

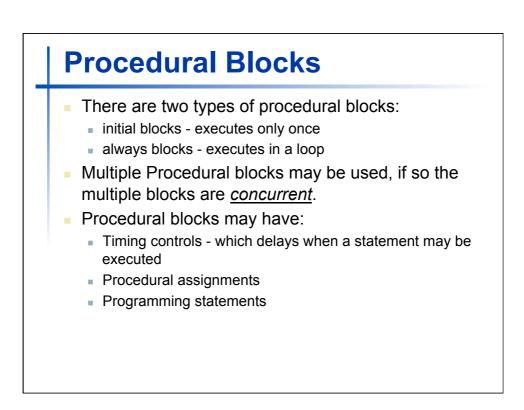

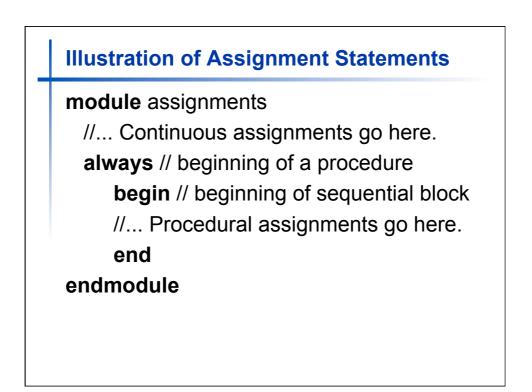

## **Procedures**

- A Verilog procedure is an always or initial statement, a task , or a function .

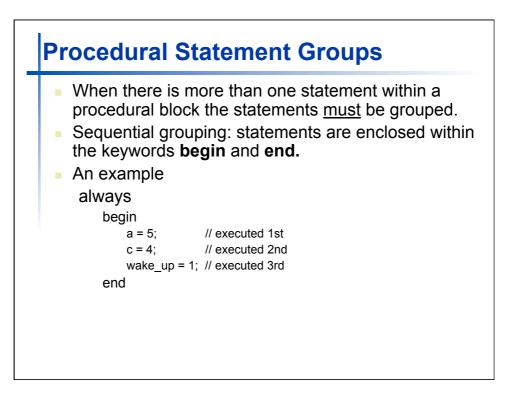

- The statements within a sequential block (statements that appear between a **begin** and an **end**) that is part of a procedure execute sequentially in the order in which they appear, but the procedure executes concurrently with other procedures.

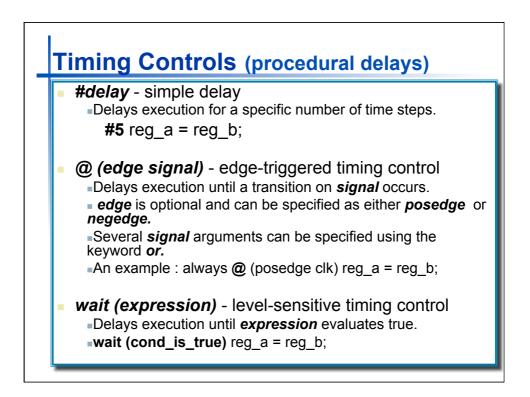

# **Control Statements**

- Two types of programming statements:

- Conditional

- Looping

- Programming statements only used in procedural blocks

| if and if-else                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| syntax:<br><i>if(expression) statement</i><br>If the expression evaluates to true then execu<br>statement group)                                                                                                                                                                                                                                                                                                                                                                        | ute the statement (or |

| <i>if(expression) statement1</i><br><i>else statement2</i><br>If the expression evaluates to true then execute statement1,<br>if false, then execute statement2 (or corresponding statement groups).                                                                                                                                                                                                                                                                                    |                       |

| <pre>module if_ex(clk);<br/>input clk;<br/>reg red,blue,pink,yellow,orange,color,green;<br/>always @ (posedge clk)<br/>if (red    (blue &amp;&amp; pink))<br/>begin<br/>\$display ("color is mixed up");<br/>color &lt;= 0; // reset the color<br/>end<br/>else if (blue &amp;&amp; yellow)<br/>\$display ("color is greenish");<br/>else if (yellow &amp;&amp; (green    orange))<br/>\$display ("not sure what color is");<br/>else \$display ("color is black");<br/>endmodule</pre> |                       |

### while

#### syntax:

### while (expression) statement or statement group

- statement or statement\_group is continuously executed as long as expression evaluates true (or non zero).

- In synthesis, the loop must contain an edge-triggered timing control, i.e. @(posedge clk) or @ (negedge clk)

module while\_ex (clk, a,b,c); input clk; input [1:0] a,b; output [1:0] c; reg [1:0] c;

always begin @ (posedge clk) while (c < b) @ (posedge clk) c = c + a; end endmodule

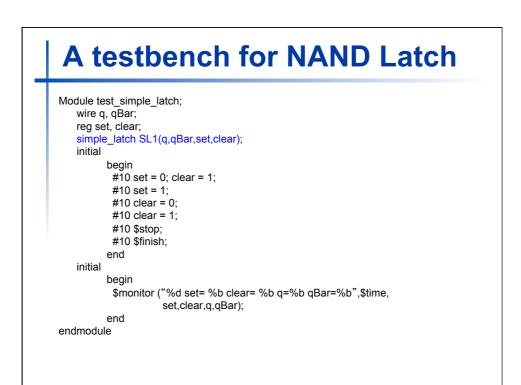

## Testbench

- A testbench generates a sequence of input values (we call these input vectors) that test or exercise the verilog code.

- It provides stimulus to the statement that will monitor the changes in their outputs.

- Testbenchs do not have a port declaration but must have an instantiation of the circuit to be tested.