## EECS4210 Architecture & Hardware for DSP

## Chapter 6

## Activity

Instructor: Prof. Peter Lian

Department of Electrical

Engineering & Computer Science

Lassonde School of Engineering

York University

## **Activity 1**

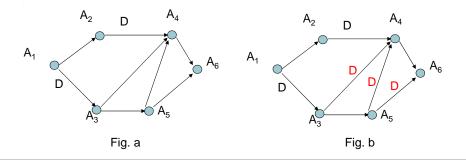

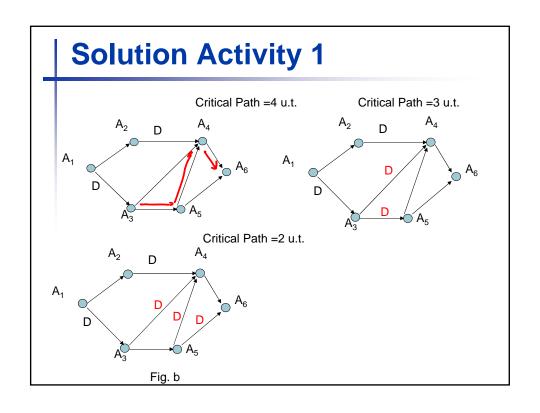

In the signal-flow graph (SFG) in Fig. a, the computation time for each node is assumed to be 1 u.t.

- (1) Calculate the critical path computation time.

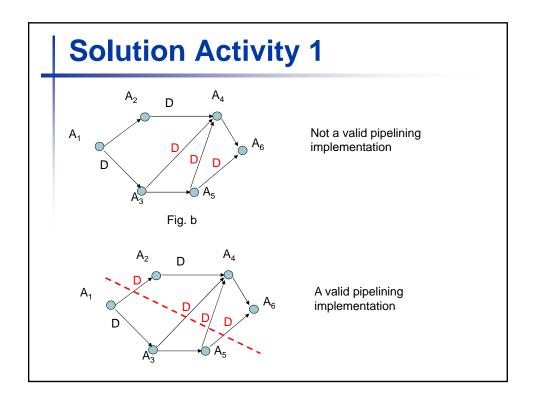

- (2) The critical path has been reduced to 2 u.t. by inserting 3 extra latches as shown in Fig. b. Is this a valid pipelining? If not, how to get a valid one.