| Processors may see different values through their caches: |                                |                                   |                                   |                                     |

|-----------------------------------------------------------|--------------------------------|-----------------------------------|-----------------------------------|-------------------------------------|

| Time                                                      | Event                          | Cache contents<br>for processor A | Cache contents<br>for processor B | Memory<br>contents fo<br>location X |

| 0                                                         |                                |                                   |                                   | 1                                   |

| 1                                                         | Processor A reads X            | 1                                 |                                   | 1                                   |

| 2                                                         | Processor B reads X            | 1                                 | 1                                 | 1                                   |

| 3                                                         | Processor A stores 0<br>into X | 0                                 | 1                                 | 0                                   |

|                                                           |                                |                                   |                                   |                                     |

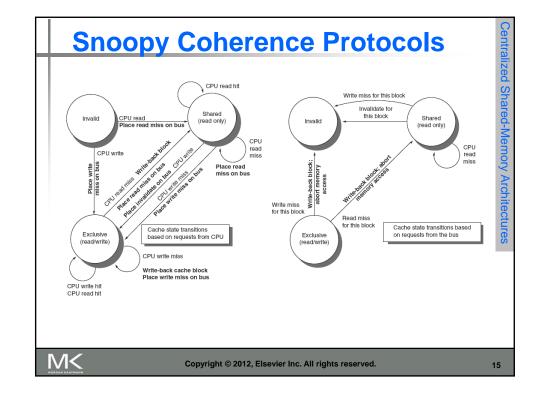

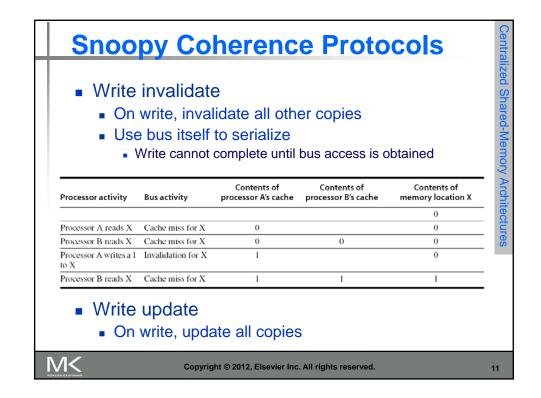

| Snoopi                          | ng Pr     | rotocols     | S                                        |             |   |

|---------------------------------|-----------|--------------|------------------------------------------|-------------|---|

|                                 | a, in thi | s case the   | exclusive a processor m<br>write invalio | nay         |   |

|                                 |           |              |                                          |             |   |

| Processor activity              | Bus       | content of A | Content of B                             | Memory      | ] |

| Processor activity              | Bus       | content of A | Content of B                             | Memory<br>0 | ] |

| Processor activity<br>A reads X | Bus       | content of A | Content of B                             | -           |   |

|                                 |           |              | Content of B                             | 0           |   |

| A reads X                       | Miss      | 0            |                                          | 0 0         |   |

| Snoopi                                                   | ng Pr       | rotocols     | S                            |             |

|----------------------------------------------------------|-------------|--------------|------------------------------|-------------|

| <ul> <li>The alterr<br/>write broa<br/>blocks</li> </ul> |             |              | write update<br>done for sha |             |

|                                                          |             |              |                              |             |

| Processor activity                                       | Bus         | content of A | Content of B                 | Memory      |

| Processor activity                                       | Bus         | content of A | Content of B                 | Memory<br>0 |

| Processor activity<br>A reads X                          | Bus<br>Miss | content of A | Content of B                 |             |

|                                                          |             |              | Content of B                 | 0           |

| A reads X                                                | Miss        | 0            |                              | 0 0         |

| Request    | Source    | State of<br>addressed<br>cache block | Type of<br>cache action | Function and explanation                                                                                                                                         |

|------------|-----------|--------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read hit   | Processor | Shared or<br>modified                | Normal hit              | Read data in local cache.                                                                                                                                        |

| Read miss  | Processor | Invalid                              | Normal miss             | Place read miss on bus.                                                                                                                                          |

| Read miss  | Processor | Shared                               | Replacement             | Address conflict miss: place read miss on bus.                                                                                                                   |

| Read miss  | Processor | Modified                             | Replacement             | Address conflict miss: write-back block, then place read miss on bus.                                                                                            |

| Write hit  | Processor | Modified                             | Normal hit              | Write data in local cache.                                                                                                                                       |

| Write hit  | Processor | Shared                               | Coherence               | Place invalidate on bus. These operations are often called<br>upgrade or <i>ownership</i> misses, since they do not fetch the data but<br>only change the state. |

| Write miss | Processor | Invalid                              | Normal miss             | Place write miss on bus.                                                                                                                                         |

| Write miss | Processor | Shared                               | Replacement             | Address conflict miss: place write miss on bus.                                                                                                                  |

| Write miss | Processor | Modified                             | Replacement             | Address conflict miss: write-back block, then place write miss on bus.                                                                                           |

| Read miss  | Bus       | Shared                               | No action               | Allow shared cache or memory to service read miss.                                                                                                               |

| Read miss  | Bus       | Modified                             | Coherence               | Attempt to share data: place cache block on bus and change state to shared.                                                                                      |

| Invalidate | Bus       | Shared                               | Coherence               | Attempt to write shared block; invalidate the block.                                                                                                             |

| Write miss | Bus       | Shared                               | Coherence               | Attempt to write shared block; invalidate the cache block.                                                                                                       |

| Write miss | Bus       | Modified                             | Coherence               | Attempt to write block that is exclusive elsewhere; write-back the cache block and make its state invalid in the local cache.                                    |