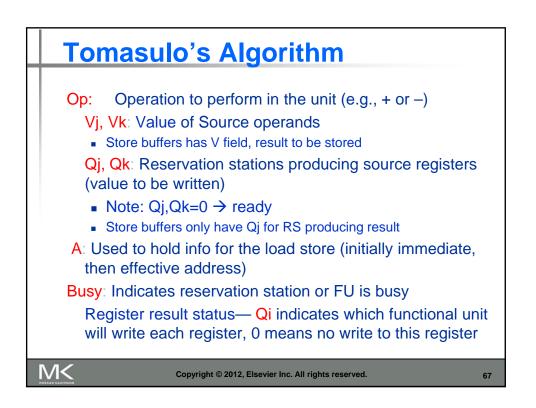

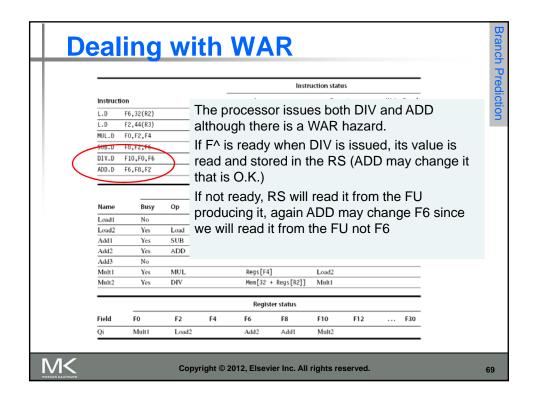

|         |           |       | _  |          | Instr          | uction statu | 15    |             |

|---------|-----------|-------|----|----------|----------------|--------------|-------|-------------|

| Instruc | tion      |       |    | Issue    |                | Exec         | cute  | Write Resu  |

| L.D     | F6,32(R2) |       |    | V        |                | 1            | 1     | Ń           |

| L.D     | F2,44(R3) |       |    | V        |                | `            | l     |             |

| MUL.D   | F0,F2,F4  |       |    | 1        |                |              |       |             |

| SUB.D   | F8,F2,F6  |       |    | V        |                |              |       |             |

| DIV.D   | F10,F0,F6 |       |    | V        |                |              |       |             |

| ADD.D   | F6,F8,F2  |       |    | V        |                |              |       |             |

|         |           |       |    | Reserv   | ation stations |              |       |             |

| Name    | Busy      | Op    | Vj | Vk       |                | Qj           | Qk    | A           |

| Load1   | No        |       |    |          |                |              |       |             |

| Load2   | Yes       | Load  |    |          |                |              |       | 44 + Regs[R |

| Add1    | Yes       | SUB   |    | Mem[32   | + Regs[R2]]    | Load2        |       |             |

| Add2    | Yes       | ADD   |    |          |                | Add1         | Load2 |             |

| Add3    | No        |       |    |          |                |              |       |             |

| Mult1   | Yes       | MUL   |    | Regs [F4 | -              | Load2        |       |             |

| Mult2   | Yes       | DIV   |    | Mem[32   | + Regs[R2]]    | Multl        |       |             |

|         |           |       |    | Regis    | ter status     |              |       |             |

| Field   | FO        | F2    | F4 | F6       | F8             | F10          | F12   | F30         |

| Qi      | Mult1     | Load2 |    | Add2     | Add1           | Mult2        |       |             |

| MIPS and ARM<br>including the A<br>Coretex A8<br>Superscalar Dynamic Hardware Dynamic Some out-of-order None at the pre-<br>execution, but no<br>speculation<br>Superscalar Dynamic Hardware Dynamic with Out-of-order execution Intel Core i3, i5 | Common name | lssue<br>structure | Hazard<br>detection | Scheduling    | Distinguishing<br>characteristic | Examples                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------|---------------------|---------------|----------------------------------|------------------------------------------------------------------|

| (dynamic) execution, but no<br>speculation<br>Superscalar Dynamic Hardware Dynamic with Out-of-order execution Intel Core i3, i5<br>(speculative) speculation with speculation AMD Phenom;                                                         |             | Dynamic            | Hardware            | Static        | In-order execution               | embedded space:<br>MIPS and ARM,<br>including the ARM            |

| (speculative) speculation with speculation AMD Phenom;                                                                                                                                                                                             |             | Dynamic            | Hardware            | Dynamic       | execution, but no                | None at the present                                              |

|                                                                                                                                                                                                                                                    |             | Dynamic            | Hardware            |               |                                  | Intel Core i3, i5, i7;<br>AMD Phenom; IBM<br>Power 7             |

| software and indicated by compiler signal processin                                                                                                                                                                                                | VLIW/LIW    | Static             |                     | Static        | and indicated by compiler        | Most examples are ir<br>signal processing,<br>such as the TI C6x |

| EPIC Primarily static Primarily Mostly static All hazards determined Itanium<br>software and indicated explicitly<br>by the compiler                                                                                                               | EPIC        | Primarily static   |                     | Mostly static | and indicated explicitly         | Itanium                                                          |

|                                  | am     | pie (                              | No S                                 | spec                                         | ulat                                  | on)     |                  |

|----------------------------------|--------|------------------------------------|--------------------------------------|----------------------------------------------|---------------------------------------|---------|------------------|

| Iteration<br>number Instructions |        | lssues at<br>clock cycle<br>number | Executes at<br>clock cycle<br>number | Memory<br>access at<br>clock cycle<br>number | Write CDB at<br>clock cycle<br>number | Comment |                  |

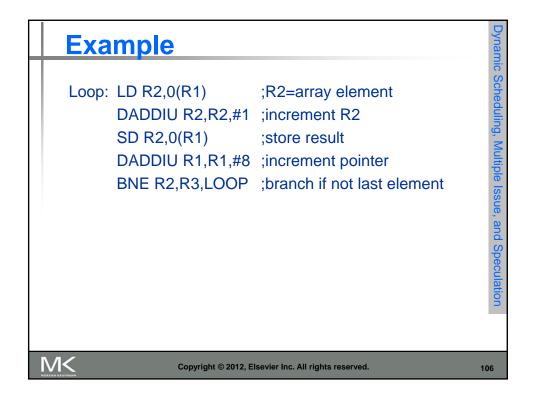

| 1                                | LD     | R2,0(R1)                           | 1                                    | 2                                            | 3                                     | 4       | First issue      |

| 1                                | DADDIU | R2,R2,#1                           | 1                                    | 5                                            |                                       | 6       | Wait for LW      |

| 1                                | SD     | R2,0(R1)                           | 2                                    | 3                                            | 7                                     |         | Wait for DADDIU  |

| 1                                | DADDIU | R1,R1,#8                           | 2                                    | 3                                            |                                       | 4       | Execute directly |

| 1                                | BNE    | R2,R3,LOOP                         | 3                                    | 7                                            |                                       |         | Wait for DADDIU  |

| 2                                | LD     | R2,0(R1)                           | 4                                    | 8                                            | 9                                     | 10      | Wait for BNE     |

| 2                                | DADDIU | R2,R2,#1                           | 4                                    | 11                                           |                                       | 12      | Wait for LW      |

| 2                                | SD     | R2,0(R1)                           | 5                                    | 9                                            | 13                                    |         | Wait for DADDIU  |

| 2                                | DADDIU | R1,R1,#8                           | 5                                    | 8                                            |                                       | 9       | Wait for BNE     |

| 2                                | BNE    | R2,R3,LOOP                         | 6                                    | 13                                           |                                       |         | Wait for DADDIU  |

| 3                                | LD     | R2,0(R1)                           | 7                                    | 14                                           | 15                                    | 16      | Wait for BNE     |

| 3                                | DADDIU | R2,R2,#1                           | 7                                    | 17                                           |                                       | 18      | Wait for LW      |

| 3                                | SD     | R2,0(R1)                           | 8                                    | 15                                           | 19                                    |         | Wait for DADDIU  |

| 3                                | DADDIU | R1,R1,#8                           | 8                                    | 14                                           |                                       | 15      | Wait for BNE     |

| 3                                | BNE    | R2,R3,LOOP                         | 9                                    | 19                                           |                                       |         | Wait for DADDIU  |

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

107

| lteration<br>number |        |            | lssues<br>at clock<br>number |    | Read access<br>at clock<br>number | Write<br>CDB at<br>clock<br>number | Commits<br>at clock<br>number | Comment           |

|---------------------|--------|------------|------------------------------|----|-----------------------------------|------------------------------------|-------------------------------|-------------------|

| 1                   | LD     | R2,0(R1)   | 1                            | 2  | 3                                 | 4                                  | 5                             | First issue       |

| 1                   | DADDIU | R2,R2,#1   | 1                            | 5  |                                   | 6                                  | 7                             | Wait for LW       |

| 1                   | SD     | R2,0(R1)   | 2                            | 3  |                                   |                                    | 7                             | Wait for DADDIU   |

| 1                   | DADDIU | R1,R1,#8   | 2                            | 3  |                                   | 4                                  | 8                             | Commit in order   |

| 1                   | BNE    | R2,R3,LOOP | 3                            | 7  |                                   |                                    | 8                             | Wait for DADDIU   |

| 2                   | LD     | R2,0(R1)   | 4                            | 5  | 6                                 | 7                                  | 9                             | No execute delay  |

| 2                   | DADDIU | R2,R2,#1   | 4                            | 8  |                                   | 9                                  | 10                            | Wait for LW       |

| 2                   | SD     | R2,0(R1)   | 5                            | 6  |                                   |                                    | 10                            | Wait for DADDIU   |

| 2                   | DADDIU | R1,R1,#8   | 5                            | 6  |                                   | 7                                  | 11                            | Commit in order   |

| 2                   | BNE    | R2,R3,LOOP | 6                            | 10 |                                   |                                    | 11                            | Wait for DADDIU   |

| 3                   | LD     | R2,0(R1)   | 7                            | 8  | 9                                 | 10                                 | 12                            | Earliest possible |

| 3                   | DADDIU | R2,R2,#1   | 7                            | 11 |                                   | 12                                 | 13                            | Wait for LW       |

| 3                   | SD     | R2,0(R1)   | 8                            | 9  |                                   |                                    | 13                            | Wait for DADDIU   |

| 3                   | DADDIU | R1,R1,#8   | 8                            | 9  |                                   | 10                                 | 14                            | Executes earlier  |

| 3                   | BNE    | R2,R3,L00P | 9                            | 13 |                                   |                                    | 14                            | Wait for DADDIU   |

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

108