## **EECS4201 Computer Architecture**

- Instructor

- Mokhtar Aboelaze

- Office LAS2026 Phone ext: 40607

- Research interests

- Computer Architecture

- Low power architecture

- Embedded systems

- FPGA (in embedded applications)

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

## **EECS4201 Computer Architecture**

- Text

- Computer Architecture: A Quantitative Approach Patterson & Hennessey 5<sup>th</sup> Ed.

- Class Meeting

- Tuesdays, Thursdays 10:11:30 CB120

- Office Hours

- Tuesdays, Thursdays 1:00-3:00pm or by appointment

M<

## **EECS4201 Topics**

- Introduction

- Instruction level parallelism

- Data level parallelism (SIMD and GPU)

- Thread level parallelism

- Memory hierarchy design

- Introduction to warehouse-scale computers

- SOC and MPSOC

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

## **Grading EECS4201**

Grades are distributed as follows

HW/Assignments

Quizzes

Midterm

Paper review – groups of 2

Final

10%

40%

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

## **Grading EECS5501**

Grades are distributed as follows

HW/Assignments

Quizzes

Midterm

Project

Final

10%

20%

35%

M<

#### **Assumptions**

- I assume that you already completed EECS2021 or equivalent (you know about these topics).

- Assembly language

- RISC architecture

- ALU architecture

- Pipelining and hazards

- Memory hierarchy and cache organization !?

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

#### **Computer Architecture**

- Why study computer architecture

- Hardware/Architecture

- Design better, faster, cheaper computers that use as little energy as possible

- Software

- Understand the architecture to squeeze as much performance for your code as possible

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

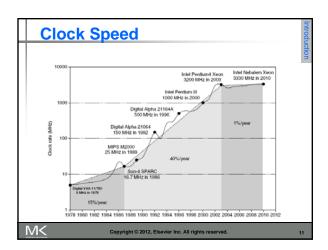

## **Computer Technology**

- Performance improvements:

- Improvements in semiconductor technology

- Feature size, clock speed

- Improvements in computer architectures

- Enabled by HLL compilers, UNIX

- Lead to RISC architectures

- Together have enabled:

- Lightweight computers

- Productivity-based managed/interpreted programming languages

M<

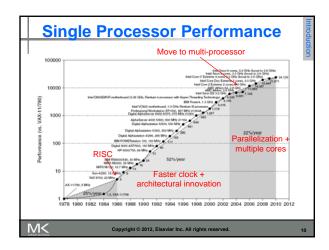

## Current Trends in Architecture ■ Cannot continue to leverage Instruction-Level parallelism (ILP) ■ Single processor performance improvement ended in 2003 ■ New models for performance: ■ Data-level parallelism (DLP) ■ Thread-level parallelism (TLP) ■ Request-level parallelism (RLP) ■ These require explicit restructuring of the application

#### **Classes of Computers**

- Personal Mobile Device (PMD)

- e.g. smart phones, tablet computers

- Emphasis on energy efficiency and real-time

- Desktop Computing

- Emphasis on price-performance

- Servers

- Emphasis on availability, scalability, throughput

- Clusters / Warehouse Scale Computers

- Used for "Software as a Service (SaaS)"

- Emphasis on availability and price-performance

- Sub-class: Supercomputers, emphasis: floating-point performance and fast internal networks

- Embedded Computers

- Emphasis: price

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

#### **Parallelism**

- Classes of parallelism in applications:

- Data-Level Parallelism (DLP)

- Task-Level Parallelism (TLP)

- Classes of architectural parallelism:

- Instruction-Level Parallelism (ILP)

- Vector architectures/Graphic Processor Units (GPUs)

- Thread-Level Parallelism Highly coupled

- Request-Level Parallelism Decoupled

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

#### Flynn's Taxonomy

- Single instruction stream, single data stream (SISD)

- Single instruction stream, multiple data streams (SIMD)

- Vector architectures

- Multimedia extensions

- Graphics processor units

- Multiple instruction streams, single data stream (MISD)

- No commercial implementation

- Multiple instruction streams, multiple data streams (MIMD)

- Tightly-coupled MIMD

- Loosely-coupled MIMD

M<

#### **Defining Computer Architecture**

- "Old" view of computer architecture:

- Instruction Set Architecture (ISA) design

- i.e. decisions regarding:

- registers, memory addressing, addressing modes, instruction operands, available operations, control flow instructions, instruction encoding

- "Real" computer architecture:

- Specific requirements of the target machine

- Design to maximize performance within constraints: cost, power, and availability

- Includes ISA, microarchitecture, hardware

Copyright © 2012, Elsevier Inc. All rights reserved.

#### Trends in Technology

Integrated circuit technology

Transistor density:

Die size:

10-20%/year

Integration overall: 40-55%/year

- DRAM capacity: 25-40%/year (slowing)

- Flash capacity: 50-60%/year

- 15-20X cheaper/bit than DRAM

- Magnetic disk technology: 40%/year

- 15-25X cheaper/bit then Flash

- 300-500X cheaper/bit than DRAM

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

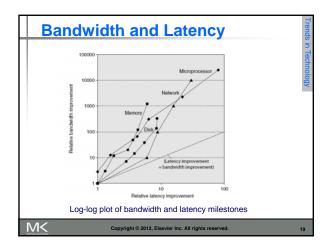

## **Bandwidth and Latency**

- Bandwidth or throughput

- Total work done in a given time

- 10,000-25,000X improvement for processors

- 300-1200X improvement for memory and disks

- Latency or response time

- Time between start and completion of an event

- 30-80X improvement for processors

- 6-8X improvement for memory and disks

#### **Transistors and Wires**

- Feature size

- Minimum size of transistor or wire in x or y dimension

- 10 microns in 1971 to .032 microns in 2011 (intel 14nm)

- Transistor performance scales linearly

- Wire delay does not improve with feature size!

- Integration density scales quadratically

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

## **Power and Energy**

- Problem: Get power in, get power out

- Power vs. Energy: Which is more important?

- Thermal Design Power (TDP)

- Characterizes sustained power consumption

- Used as target for power supply and cooling system

- Lower than peak power, higher than average power consumption

- Clock rate can be reduced dynamically to limit power consumption

- Energy per task is often a better measurement

M<

## **Dynamic Energy and Power**

- Dynamic energy

- Transistor switch from  $0 \rightarrow 1$  or  $1 \rightarrow 0$

- ½ x Capacitive load x Voltage²

- Dynamic power

- ½ x Capacitive load x Voltage² x Frequency switched

- Reducing clock rate reduces power, not energy

M/<

Copyright © 2012, Elsevier Inc. All rights reserved.

#### **Power**

- Intel 80386 consumed ~ 2 W

- 3.3 GHz Intel Core i7 consumes 130 W

- Heat must be dissipated from 1.5 x 1.5 cm chip

- This is the limit of what can be cooled by air

- Hot spot ?

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

## **Reducing Power**

- Techniques for reducing power:

- Do nothing well

- Dynamic Voltage-Frequency Scaling

- Design for typical case: for example PMD are idle most of the time, low power state for DRAM, disks

- Overclocking, turning off cores

M<

#### **Static Power**

- Static power consumption

- Current<sub>static</sub> x Voltage

- Leakage current (power could be as high as 50% of total power consumption) increases with decreasing the transistor size (λ)

- Scales with number of transistors

- To reduce: power gating

N/I<

Copyright © 2012, Elsevier Inc. All rights reserved.

#### **Trends in Cost**

- Cost driven down by learning curve

- Yield

- DRAM: price closely tracks cost

- Microprocessors: price depends on volume

- 10% less for each doubling of volume

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

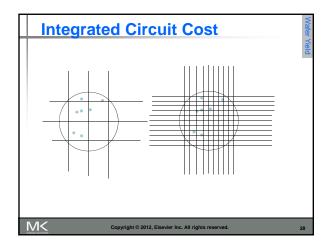

#### **Integrated Circuit Cost**

Integrated circuit

$Cost of integrated circuit \equiv \frac{Cost of die + Cost of testing die + Cost of packaging and final test}{Final test yield}$

Cost of die = Cost of wafer

Dies per wafer × Die yield

Dies per wafer =  $\frac{\pi \times (\text{Wafer diameter/2})^2}{\text{Die area}} - \frac{\pi \times \text{Wafer diameter}}{\sqrt{2 \times \text{Die area}}}$

Bose-Einstein formula:

Die yield = Wafer yield  $\times 1/(1 + Defects per unit area \times Die area)^N$

- Defects per unit area = 0.016-0.057 defects per square cm (2010)

- N = process-complexity factor = 11.5-15.5 (40 nm, 2010)

M<

## ■ Service Level Agreement (SLA) guarantees a certain level of dependability. ■ Module reliability ■ Mean time to failure (MTTF) ■ Mean time between failures (MTBF) = MTTF + MTTR ■ Availability = MTTF / (MTTF+MTTR) ■ Cost of failure: varies hugely depending on applications

| ■ Example  10 disks 1,000,000-hour MTTF                                                                                                              |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1 ATA controller 500,000-hour MTTF 1 Power supply 200,000-hour MTTF                                                                                  |   |

| 1 Fan 200,000-hour MTTF  ATA cable 1,000,000-hour MTTF  Acquired lifetimes are expensationly                                                         |   |

| <ul> <li>Assume lifetimes are exponentially<br/>distributed and failures are independent</li> </ul>                                                  |   |

| ■ Calculate MTTF                                                                                                                                     |   |

| M  Copyright © 2012, Elsevier Inc. All rights reserved. 31                                                                                           |   |

|                                                                                                                                                      |   |

|                                                                                                                                                      |   |

|                                                                                                                                                      | ] |

|                                                                                                                                                      |   |

| ■ What if we added one extra power supply                                                                                                            |   |

|                                                                                                                                                      |   |

|                                                                                                                                                      |   |

|                                                                                                                                                      |   |

|                                                                                                                                                      |   |

| Copyright © 2012, Elsevier Inc. All rights reserved.                                                                                                 |   |

|                                                                                                                                                      |   |

|                                                                                                                                                      |   |

| Measuring Performance                                                                                                                                | 1 |

| Typical performance metrics:                                                                                                                         |   |

| Response time Throughput                                                                                                                             |   |

| Speedup of X relative to Y     Execution time <sub>Y</sub> / Execution time <sub>X</sub>                                                             |   |

| Execution time     Wall clock time: includes all system overheads     CPU time: only computation time                                                |   |

| <ul><li>Benchmarks</li></ul>                                                                                                                         |   |

| Kernels (e.g. matrix multiply)     Toy programs (e.g. sorting)     Synthetic benchmarks (e.g. Dhrystone)     Benchmark suites (e.g. SPEC06fp, TPC-C) |   |

| Copyright © 2012, Elsevier Inc. All rights reserved.                                                                                                 |   |

#### benchmarks

- Embedded Microprocessor Benchmark Consortium

- www.eembc.org

- 41 kernels

- SPEC: Standard Performance Evaluation Corporation

- www.spec.org

- Covers many application classes (desktop, SPEC Web, SPECFS)

- TPC: Transaction Processing Council

- www.tpc.org

- Database transactions

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

## **Reporting Performance**

Many programs, how can we capture performance using a single number?

P1

P2

P3

Machine-A

10

8

25

Machine-B

12

9

20

Machine-C

8

8

30

- Sum of execution time

- Sum of weighted execution time

- Geometric mean of execution time

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

## **Reporting Performance**

Many programs, how can we capture performance using a single number?

P1

P2

P3

Machine-A

10

8

25

Machine-B

12

9

20

Machine-C

8

8

30

- Sum of execution time

- Sum of weighted execution time

- Geometric mean of execution time

M<

## **Reporting Performance**

Many programs, how can we capture performance using a single number?

P1

P2

P3

Machine-A

10

8

25

Machine-B

12

9

20

Machine-C

8

8

30

- Sum of execution time

- Sum of weighted execution time

- Geometric mean of execution time

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

## **Reporting Performance**

machine\_A

M/C\_B

M/C\_C

P1

1sec

10sec

20sec

P2

1000sec

100sec

20sec

M<

Copyright © 2012, Elsevier Inc. All rights reserved.

## **Reporting Performance**

- Time =  $TC \times CPI \times IC$

- Must be reproducible

- Complete description of the computer and compiler flags.

- Usually, compared to a standard machine execution time SPECRatioA = T<sub>ref</sub>/T<sub>A</sub>.

- Geometric mean

M<

|             | <b>C2006 for</b>              | Op     | LCI           | UII     | A+ 4      |          |         |

|-------------|-------------------------------|--------|---------------|---------|-----------|----------|---------|

|             |                               |        |               |         |           |          |         |

|             |                               |        |               |         |           |          |         |

| Name        | Description                   | IC×109 | CPI           | Tc (ns) | Exec time | Ref time | SPECraf |

| perl        | Interpreted string processing | 2,118  | 0.75          | 0.40    | 637       | 9,777    | 15      |

| bzip2       | Block-sorting compression     | 2,389  | 0.85          | 0.40    | 817       | 9,650    | 11      |

| gcc         | GNU C Compiler                | 1,050  | 1.72          | 0.47    | 24        | 8,050    | 11      |

| mcf         | Combinatorial optimization    | 336    | 10.00         | 0.40    | 1,345     | 9,120    | 6       |

| go          | Go game (AI)                  | 1,658  | 1.09          | 0.40    | 721       | 10,490   | 14      |

| hmmer       | Search gene sequence          | 2,783  | 0.80          | 0.40    | 890       | 9,330    | 10      |

| sjeng       | Chess game (Al)               | 2,176  | 0.96          | 0.48    | 37        | 12,100   | 14      |

| libquantum  | Quantum computer simulation   | 1,623  | 1.61          | 0.40    | 1,047     | 20,720   | 19      |

| h264avc     | Video compression             | 3,102  | 0.80          | 0.40    | 993       | 22,130   | 22      |

| omnetpp     | Discrete event simulation     | 587    | 2.94          | 0.40    | 690       | 6,250    | 9       |

| astar       | Games/path finding            | 1,082  | 1.79          | 0.40    | 773       | 7,020    | 9       |

| xalancbmk   | XML parsing                   | 1,058  | <b>1</b> 2.70 | 0.40    | 1,143     | 6,900    | 6       |

| Geometric m | Geometric mean                |        |               |         |           | 11.7     |         |

|             | High cache miss rate          | es /   |               |         |           |          |         |

|             | riigir cacric miss ratt       |        |               |         |           |          |         |

| Name        | Description                   | IC×109 | CPI  | Tc (ns) | Exec time | Ref time | SPECratio |

|-------------|-------------------------------|--------|------|---------|-----------|----------|-----------|

| perl        | Interpreted string processing | 2,252  | 0.60 | 0.376   | 508       | 9,770    | 19.2      |

| bzip2       | Block-sorting compression     | 2,390  | 0.70 | 0.376   | 629       | 9,650    | 15.4      |

| gcc         | GNU C Compiler                | 794    | 1.20 | 0.376   | 358       | 8,050    | 22.5      |

| mcf         | Combinatorial optimization    | 221    | 2.66 | 0.376   | 221       | 9,120    | 41.2      |

| go          | Go game (AI)                  | 1,274  | 1.10 | 0.376   | 527       | 10,490   | 19.9      |

| Hmmer       | Search gene sequence          | 2,616  | 0.60 | 0.376   | 590       | 9,330    | 15.8      |

| sjeng       | Chess game (AI)               | 1,948  | 0.80 | 0.376   | 586       | 12,100   | 20.7      |

| libquantum  | Quantum computer simulation   | 659    | 0.44 | 0.376   | 109       | 20,720   | 190.0     |

| h264avc     | Video compression             | 3,793  | 0.50 | 0.376   | 713       | 22,130   | 31.0      |

| omnetpp     | Discrete event simulation     | 367    | 2.10 | 0.376   | 290       | 6,250    | 21.5      |

| astar       | Games/path finding            | 1,250  | 1.00 | 0.376   | 470       | 7,020    | 14.9      |

| xalancbmk   | XML parsing                   | 1,045  | 0.70 | 0.376   | 275       | 6,900    | 25.1      |

| Geometric m | ean                           |        |      |         |           |          | 25.7      |

## SPEC Power Benchmark ■ Power consumption of server at different workload levels ■ Performance: ssj\_ops/sec ■ Power: Watts (Joules/sec) Overall ssj\_ops per Watt = \( \bigcup\_{i=0}^{10} \ssj\_ops\_i \right) / \( \bigcup\_{i=0}^{10} \text{power}\_i \)

|                  | ver_ssj2008               |                      |

|------------------|---------------------------|----------------------|

| Target Load %    | Performance (ssj_ops/sec) | Average Power (Watts |

| 100%             | 231,867                   | 295                  |

| 90%              | 211,282                   | 286                  |

| 80%              | 185,803                   | 275                  |

| 70%              | 163,427                   | 265                  |

| 60%              | 140,160                   | 256                  |

| 50%              | 118,324                   | 246                  |

| 40%              | 920,35                    | 233                  |

| 30%              | 70,500                    | 222                  |

| 20%              | 47,126                    | 206                  |

| 10%              | 23,066                    | 180                  |

| 0%               | 0                         | 141                  |

| Overall sum      | 1,283,590                 | 2,605                |

| ∑ssj_ops/ ∑power |                           | 493                  |

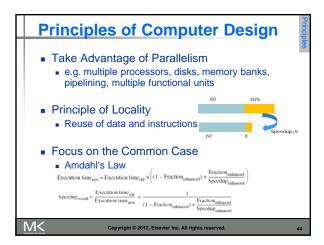

# Principles of Computer Design The Processor Performance Equation CPU time = CPU clock cycles for a program × Clock cycle time CPU time = CPU clock cycles for a program Clock rate CPI = CPU clock cycles for a program Instruction count CPU time = Instruction count × Cycles per instruction × Clock cycle time Instructions × Clock cycles × Seconds Program × Clock cycles × Seconds Program = CPU time

| <b>Princi</b> | ples | of | Com | puter | Desi | iar  |

|---------------|------|----|-----|-------|------|------|

|               |      |    |     |       |      | . 3- |

Different instruction types having different CPIs

$$CPU clock cycles = \sum_{i=1}^{n} IC_i \times CPI_i$$

CPU time =

$$\left(\sum_{i=1}^{n} IC_i \times CPI_i\right) \times Clock$$

cycle time

M<

| Examp | ole | Example |

|-------|-----|---------|

|       |     |         |

|       |     |         |

|       |     |         |

|       |     |         |

|       |     |         |

| M     |     |         |

| Example | )                                                    | Example |

|---------|------------------------------------------------------|---------|

|         |                                                      | e       |

|         |                                                      |         |

|         |                                                      |         |

|         |                                                      |         |

|         |                                                      |         |

|         |                                                      |         |

|         |                                                      |         |

| M<      | Copyright © 2012, Elsevier Inc. All rights reserved. | 48      |

| Fallacies and Pitfalls                               |  |

|------------------------------------------------------|--|

|                                                      |  |

|                                                      |  |

|                                                      |  |

|                                                      |  |

|                                                      |  |

| Copyright © 2012, Elsevier Inc. All rights reserved. |  |