# EECS3611 Analog Integrated Circuit Design

Textbook

Design of Analog CMOS Integrated Circuits

2<sup>nd</sup> Edition, Copyright: 2017

By: Behzad Razavi

McGraw Hill Education

ISBN-10: 0072524936

ISBN-13: 9780072524932

Available at York Bookstore

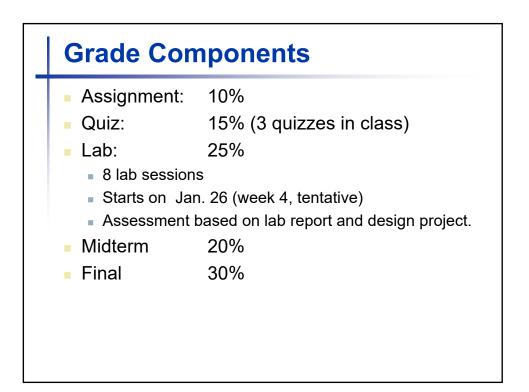

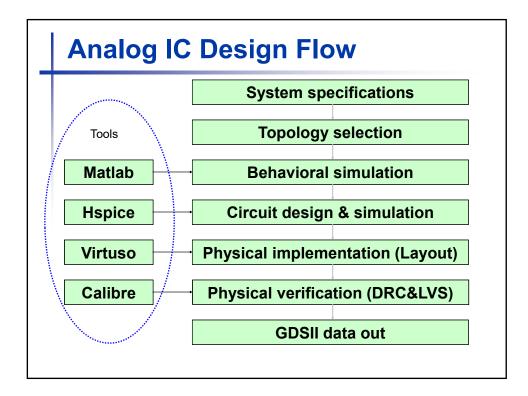

# LAB

- Lab will be at BEL 334

- Lab contains two parts

- Part 1 is for learning of EDA tool (i.e. Cadence), circuit simulation, and layout.

- Part 2 is for a design project.

- Maintain a laboratory book or journal for all lab sessions. It must be signed by the TA before you leave the lab.

# **Topics covered**Introduction to analog design Basic MOS device physics Single state amplifiers Layout and design rules Differential amplifiers Passive and active current mirrors Frequency response of amplifiers Noise Feedback Operational amplifiers

- After successful completion of the course, students are expected to be able to:

- To analyze the characteristics of basic analog integrated circuits

- To formulate the behavior of basic analog circuits by inspection

- To perform circuit simulation using computer-aided tool

- To draw layout based on given design rules

# **Models for Design**

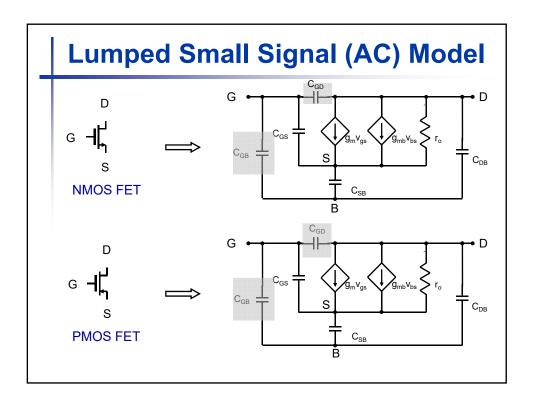

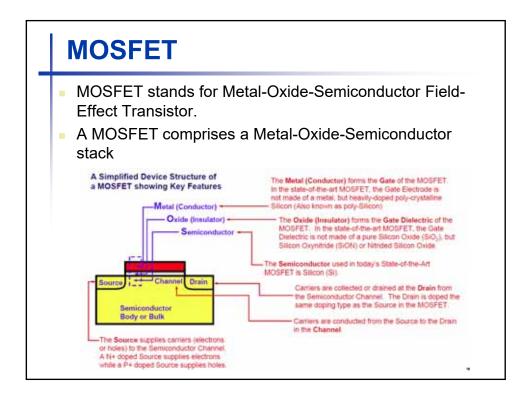

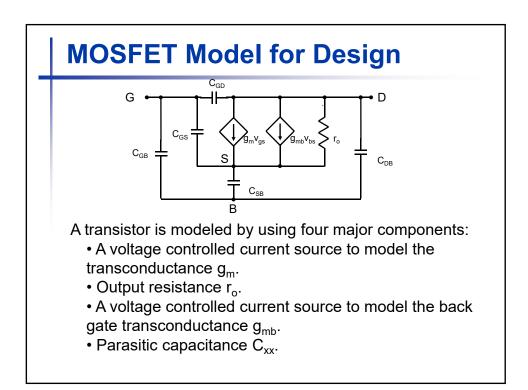

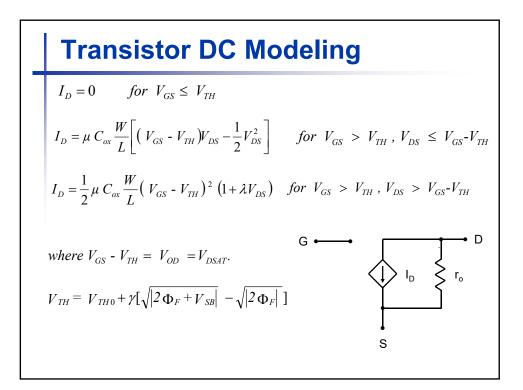

- Transistor is modeled using basic circuit components.

- Two types of models: large signal model and small signal model

- Large signal model large signal low frequency, such as DC bias points.

- Small signal model small signal and parameters such as gain and frequency response of an analog circuit.

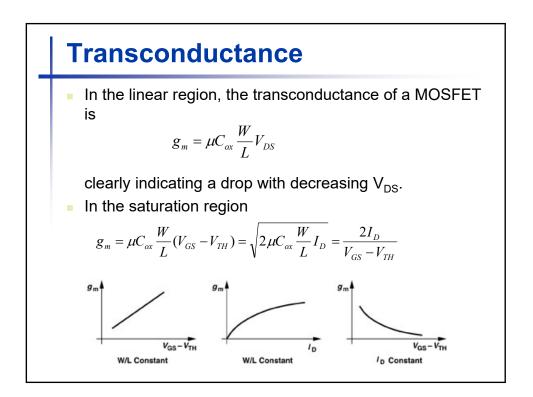

### Transconductance

The effect of gate voltage controlling the drain current is modeled by transconductance

$$g_m = \frac{\partial I_D}{\partial V_{GS}}$$

- Hence this g<sub>m</sub> models how drain current will change with change in gate voltage.

- The transconductance is the most important parameter of a transistor in analog circuit design.

- This effect is modeled as a voltage controlled current source between drain and source.

# **Output Conductance**

The effect of the drain voltage is modeled using the output conductance

$$g_d = \frac{\partial I_D}{\partial V_{DS}}$$

- This models how I<sub>D</sub> changes when the V<sub>DS</sub> changes. Since we want only input voltage to control I<sub>D</sub> and not the output voltage, ideally, this should be zero.

- Hence in saturation region using I<sub>D</sub> expression:

$$I_D = \frac{1}{2} \mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS}) \rightarrow g_d = \frac{\partial I_D}{\partial V_{DS}} \approx \lambda I_D$$

This effect is captured as a resistance called output resistance:

$$r_o = \frac{1}{g_d} = \frac{1}{\lambda I_D}$$

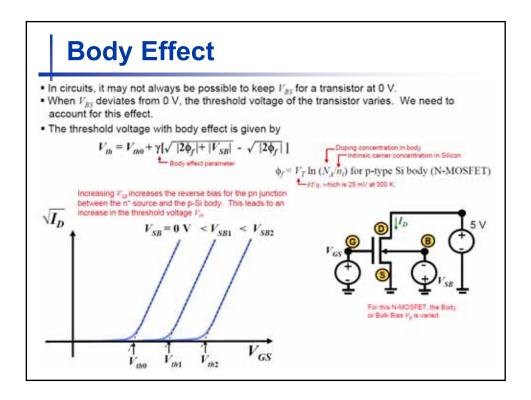

### **Back Gate Transconductance**

The effect of body bias or bulk voltage is modeled using body or back gate transconductance.

$$g_{mb} = \frac{\partial I_D}{\partial V_{BS}}$$

Hence this value is mainly determined by γ. This effect is captured as a dependent current source circuit element between drain and source.

$$g_{mb} = \frac{\partial I_D}{\partial V_{BS}} = g_m \frac{\gamma}{2\sqrt{2\Phi_F + V_{SB}}} = \eta g_n$$

Normally the back gate transconductance is 20% of the front gate transconductance, i.e. η=0.2.

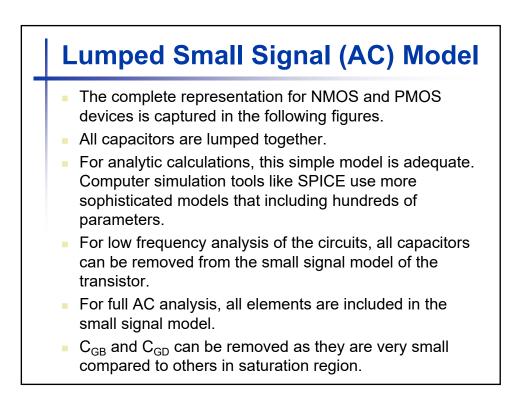

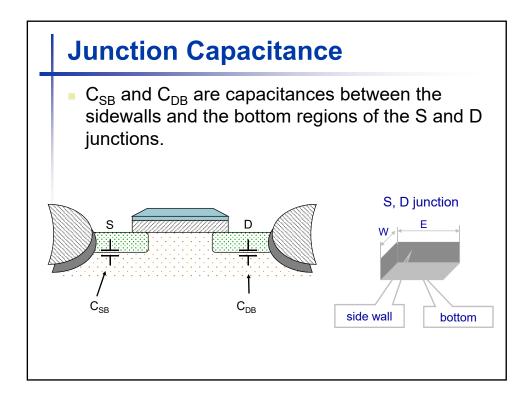

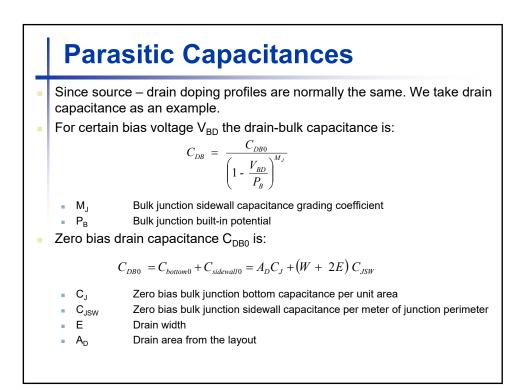

# **MOSFET Capacitance**

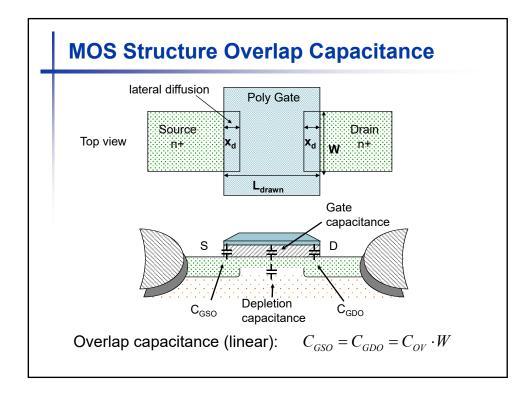

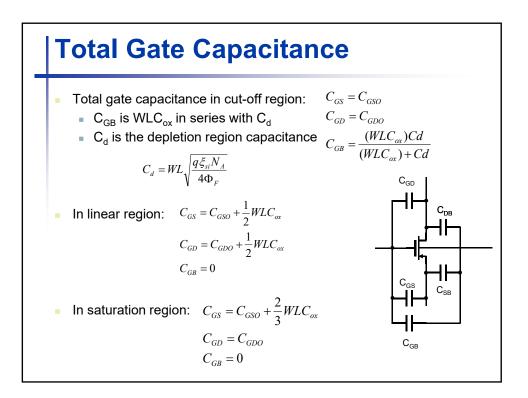

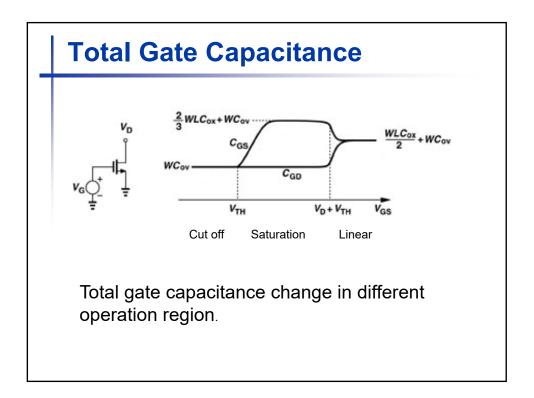

The fundamental mode of MOSFET operation is through charge which is modeled through 3 non-linear bias dependent capacitances  $C_{GS}$ ,  $C_{GD}$  and  $C_{GB}$ .

In addition, there are three linear overlap capacitances.

- C<sub>GSO</sub>: Gate to source overlap capacitance per meter of channel width. This and drain overlap capacitance are independent of length L as they are associated with edge effects.

- C<sub>GDO</sub> : Similar to drain counterpart.

- C<sub>GBO</sub>: Gate to bulk overlap capacitance per meter of channel length and is associated with edge effects at the width ends of the gate area.

# **Parasitic Resistances**

- R<sub>S</sub> and R<sub>D</sub> are the source and drain resistances due to which inside source and drain voltages applied to actual inversion layer will change for high drain current.

- In addition, there are noise coefficients which may add some noise to I<sub>D</sub>.

- This model ignores many parasitic resistances, bipolar devices and PNPN devices.