# Virtuoso AMS Designer Environment Tutorials

Product Version 6.1.6 March 2014 © 2006–2013 Cadence Design Systems, Inc. All rights reserved.

Portions © Regents of the University of California, Sun Microsystems, Inc., Scriptics Corporation. Used by permission.

Printed in the United States of America.

Cadence Design Systems, Inc. (Cadence), 2655 Seely Ave., San Jose, CA 95134, USA.

The AMS Designer simulator contains technology licensed from, and copyrighted by: Regents of the University of California, Sun Microsystems, Inc., Scriptics Corporation, and other parties and is © 1989-1994 Regents of the University of California, 1984, the Australian National University, 1990-1999 Scriptics Corporation, and other parties. All rights reserved.

Open SystemC, Open SystemC Initiative, OSCI, SystemC, and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission.

MMSIM contains technology licensed from, and copyrighted by: C. L. Lawson, R. J. Hanson, D. Kincaid, and F. T. Krogh © 1979, J. J. Dongarra, J. Du Croz, S. Hammarling, and R. J. Hanson © 1988, J. J. Dongarra, J. Du Croz, I. S. Duff, and S. Hammarling © 1990; University of Tennessee, Knoxville, TN and Oak Ridge National Laboratory, Oak Ridge, TN © 1992-1996; Brian Paul © 1999-2003; M. G. Johnson, Brisbane, Queensland, Australia © 1994; Kenneth S. Kundert and the University of California, 1111 Franklin St., Oakland, CA 94607-5200 © 1985-1988; Hewlett-Packard Company, 3000 Hanover Street, Palo Alto, CA 94304-1185 USA © 1994, Silicon Graphics Computer Systems, Inc., 1140 E. Arques Ave., Sunnyvale, CA 94085 © 1996-1997, Moscow Center for SPARC Technology, Moscow, Russia © 1997; Regents of the University of California, 1111 Franklin St., Oakland, CA 94607-5200 © 1990-1994, Sun Microsystems, Inc., 4150 Network Circle Santa Clara, CA 95054 USA © 1994-2000, Scriptics Corporation, and other parties © 1998-1999; Aladdin Enterprises, 35 Efal St., Kiryat Arye, Petach Tikva, Israel 49511 © 1999 and Jean-loup Gailly and Mark Adler © 1995-2005; RSA Security, Inc., 174 Middlesex Turnpike Bedford, MA 01730 © 2005.

All rights reserved.

Associated third party license terms may be found at *install\_dir/doc/OpenSource/\**

**Trademarks**: Trademarks and service marks of Cadence Design Systems, Inc. contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 800.862.4522. All other trademarks are the property of their respective holders.

**Restricted Permission:** This publication is protected by copyright law and international treaties and contains trade secrets and proprietary information owned by Cadence. Unauthorized reproduction or distribution of this publication, or any portion of it, may result in civil and criminal penalties. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. Unless otherwise agreed to by Cadence in writing, this statement grants Cadence customers permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used only in accordance with a written agreement between Cadence and its customer.

- 2. The publication may not be modified in any way.

- 3. Any authorized copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement.

- 4. The information contained in this document cannot be used in the development of like products or software, whether for internal or external use, and shall not be used for the benefit of any other party, whether or not for consideration.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. Except as may be explicitly set forth in such agreement, Cadence does

not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor

# Contents

| <u>1</u>                                                     |

|--------------------------------------------------------------|

| Understanding AMS Designer Simulator Use Models 7            |

| <u>2</u>                                                     |

| <u>Before You Begin</u> 13                                   |

| 3                                                            |

| Building an AMS Test Case in ADE 17                          |

| <u>4</u>                                                     |

| T<br>Migrating to AMS Designer 69                            |

| <u>5</u>                                                     |

| Migrating to the OSS Netlister 129                           |

| <u>6</u>                                                     |

| Using Inherited Connections for Multiple Power Supply Design |

| 137                                                          |

| 7                                                            |

| <u>7</u>                                                     |

Using Digital Disciplines for Multiple Power Supply Design 157

# 1

# Understanding AMS Designer Simulator Use Models

The Virtuoso<sup>®</sup> AMS Designer simulator is a single executable for language-based mixed-signal simulation. You can use the AMS Designer simulator to design and verify large and complex mixed-signal SoCs (systems on chips) and multichip designs. The two primary use models for the AMS Designer simulator are:

AMS Designer Virtuoso use model

For schematic-based, analog-centric designs, run the AMS Designer simulator from the Virtuoso Analog Design Environment (ADE) using the <u>OSS netlister</u> and <u>irun</u>.

AMS Designer Incisive use model

For digital-centric design verification, run the AMS Designer simulator from the command line using irun. This use model takes advantage of the power of the amsd block. For more information using irun and the amsd block for AMS simulation, see the *Virtuoso AMS Designer Simulator User Guide*. For tutorials that focus on this use model, see *Virtuoso AMS Designer Simulator Tutorials*.

Both use models feature the simulation front end (SFE) parser, which is the same parser that the Spectre circuit simulator uses.

The tutorials in this document focus on the AMS Designer Virtuoso use model (sometimes abbreviated as AVUM).

# Important

Before running these tutorials, verify that your AMS Designer installation is set up and working. See also <u>"Before You Begin"</u> on page 13.

See also the following topics:

- Benefits of Using the OSS Netlister on page 8

- Important Considerations when Using the OSS Netlister on page 9

# **Benefits of Using the OSS Netlister**

Using the OSS netlister means

- You do not need to convert Spectre PDKs to use the AMS simulator (because the OSS netlister uses Spectre CDF and simInfo, which is compatible with the AMS Designer simulator)

- You do not have to re-netlist the parts of your design that you have not changed (because the OSS netlister is an incremental netlister)

- You do not have to have writable master libraries and you do not have to use explicit or implicit TMP directories (because the OSS netlister does not write to the Cadence "5x" library/cell/view structure)

- You can run standalone simulations and debug more simply (because the OSS netlister writes a single netlist to one location)

- The compilation step is faster (because the OSS netlister does not use the "5x" structure)

- You can use irun, which is consistent with the digital use model such that you can share design information

- You can have VHDL modules in your design

- Your VHDL modules must be at the leaf level only

- □ You cannot use instance binding for VHDL modules

For information about instance binding, see the <u>Cadence Hierarchy Editor User</u> <u>Guide</u>.

### Important Considerations when Using the OSS Netlister

See the following topics for important considerations when using the OSS netlister:

- <u>Netlisting Text Views</u> on page 9

- Using View Lists and Stop Lists on page 10

- Netlisting the Symbol View for an Instance as Analog or Digital on page 10

- <u>Netlisting Inherited Connections</u> on page 11

- Updating Text Views that Do Not Have Design Database Information on page 11

- <u>Selecting irun for Simulation</u> on page 12

### **Netlisting Text Views**

To netlist a text view, you must import the text view into the Cadence "5x" library/cell/view structure, or the text view must contain Virtuoso database files (.oa). You can satisfy this requirement using any of the following methods:

**Note:** If you have Verilog or VHDL text files that you do not want to netlist, you can specify them by clicking *Library Files/Directories* on the *Main* tab in the AMS Options form.

■ Import Verilog text files using the Verilog In utility.

For more information about using Verilog In, see the Verilog In for Virtuoso Design Environment User Guide and Reference.

■ Import VHDL text files using the VHDL In utility.

For more information about using VHDL In, see the VHDL In for Virtuoso Design Environment User Guide and Reference.

- In the schematic editor, choose *Create Cellview From Cellview*.

- In the command interpreter window (CIW), choose *File New Cellview*.

- In the Library Manager window, open the cell for editing and then save it.

**Note:** If you were previously using the cellview-based netlister and you do not know which cells do not have a Virtuoso database file (.oa), or if you have many views that do not have a database file, see <u>"Updating Text Views that Do Not Have Design Database Information"</u> on page 11.

### **Using View Lists and Stop Lists**

Cadence software uses configuration view lists and stop lists to determine how to netlist design cells. Each cell in your design must have an associated schematic or simulator primitive. You specify valid views, in order of preference, in your view list. The netlister netlists cells that are leaf nodes in the design hierarchy according to the views you specify in the stop list. You specify the views that correspond to the most detailed simulation descriptions for a cell in the stop list. For each instance view in your design, the netlister stops the design hierarchy expansion process when it encounters a matching view in the stop list and writes that information to the netlist.

In the Cadence Hierarchy Editor, you can specify global bindings as well as view binding at the instance level. You can specify instance-level view binding if you want to netlist using a different view for a particular instance of a cell.

**Note:** For more information about configuration views, see <u>"Understanding Configurations"</u> in the *Virtuoso*<sup>®</sup> *AMS Designer Environment User Guide*. For more information about view lists and stop lists, see the <u>Cadence Hierarchy Editor User Guide</u>.

### Netlisting the Symbol View for an Instance as Analog or Digital

By default, if you bind an instance to a symbol view in your configuration, the netlister netlists that instance as digital. To netlist such an instance instead as an analog primitive using the Spectre CDF simulation information, do one of the following:

- In the Virtuoso<sup>®</sup> Hierarchy Editor:

- **a.** Open your configuration.

- **b.** Replace symbol with spectre in the *View List* and *Stop List* fields.

- In ADE:

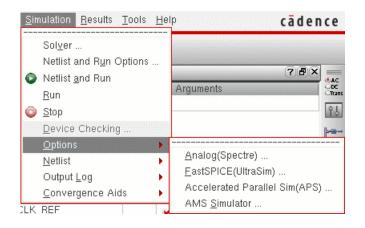

- a. Choose Simulation Options AMS Simulator,

The AMS Options form appears.

- **b.** Select the *Netlister* tab.

- c. In the Netlist using spectre CDF simInfo field, type symbol.

### **Netlisting Inherited Connections**

An inherited connection is a net expression associated with either a signal or a terminal. You use inherited connections to override specific global names in your design. You can use this feature for a design that has more than one power supply.

To implement separate power supplies (such as analog and digital, or +3 Volts and +5 Volts), do the following:

- **1.** Assign net expressions to those global signals whose default values you might want to override.

- 2. Use netSet properties to specify new values for those signals.

**Note:** For more information about inherited connections and netSet properties, see <u>"Inherited Connections"</u> in the <u>Virtuoso Schematic Editor L User Guide</u>.

### Updating Text Views that Do Not Have Design Database Information

The OSS-based AMS netlister does not support designs with text-only views; that is, text views that do not contain a Virtuoso<sup>®</sup> database file (.oa). You can create the .oa database for such views by doing the following:

**1.** In ADE, choose *Tools – Update Text Views*.

The Update Text Views form appears.

- 2. Select Create database for text views.

- **3.** In the *Text views* group box, specify the text view or views for which you want to create the Virtuoso database.

- 4. Click OK.

### Selecting irun for Simulation

You can use irun for single-step compilation, elaboration, and simulation of your mixed-signal designs. AMS Designer relies on the OSS-based netlister to netlist designs for irun simulation. For OSS-based netlisting, you must run AMS from the Virtuoso<sup>®</sup> Analog Design Environment (ADE) and do the following:

**1.** Choose Setup – Simulator.

The Choosing Simulator/Directory/Host form appears.

- 2. Select *ams* from the *Simulator* drop-down combo box.

- **3.** Click *OK*.

- 4. Choose Simulation Netlist and Run Options.

The Netlist and Run Options form appears.

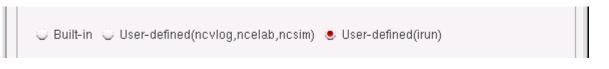

- 5. In the NETLIST AND RUN MODE section, select OSS-based netlister with irun.

- 6. Click *OK*.

**Note:** For more information about the OSS netlister, see <u>"Using the OSS Netlister"</u> in the *Virtuoso AMS Designer Environment User Guide*. For more information about irun simulation, see "Using irun for AMS Simulation" in the *Virtuoso AMS Designer Simulator User Guide*.

# **Before You Begin**

**Note:** ADE is an abbreviation for the Virtuoso<sup>®</sup> Analog Design Environment. HED is an abbreviation for the Virtuoso Hierarchy Editor. AMS-Spectre stands for the AMS Designer simulator with the Spectre solver. AMS-UltraSim stands for the AMS Designer simulator with the UltraSim solver.

You can run these tutorials using the AMS Designer simulator along with Cadence<sup>®</sup> Virtuoso<sup>®</sup> software—such as the Virtuoso Analog Design Environment (ADE) and the Virtuoso Hierarchy Editor—from the IC 6.1.2 ISR 14 release or later. Your MMSIM installation must be version 7.0 or later.

Make sure your paths and environment variables are set up to use the correct releases. For example:

```

setenv CDSHOME /cds/tools/IC612

setenv AMSHOME /cds/tools/ius82

set path= ( $AMSHOME/tools/dfII/bin $AMSHOME/tools/bin $path)

set path = ( $CDSHOME/tools/bin $CDSHOME/tools/dfII/bin

$CDSHOME/tools/dfII/pvt/bin $path)

```

You can download the tutorial files from the installation hierarchy:

```

your_install_dir/tools/dfII/samples/tutorials/AMS/

```

To download all tutorials, do the following:

1. Create a tutorial directory in your local area. For example:

mkdir myAmsTutorials

2. Copy the tutorial files from the installation hierarchy. For example:

cp -r \$CDSHOME/tools/dfII/samples/tutorials/AMS/\* myAmsTutorials

The system copies all the tutorial files from samples/tutorials/AMS into myAmsTutorials.

3. Change to your local tutorials directory. For example:

cd myAmsTutorials

4. Decompress each tutorial file. For example, to decompress the AMSDINADE.tar.gz file, do the following:

```

gunzip AMSDInADE.tar.gz

tar xf AMSDInADE.tar

```

To download only a particular tutorial, do the following:

**1.** Change to the directory where you want to download the tutorial. For example:

```

cd myAmsTutorials

```

2. Copy the tutorial file from the installation hierarchy. For example:

cp -r \$CDSHOME/tools/dfII/samples/tutorials/AMS/AMSDInADE.tar.gz .

The system copies the AMSDInADE.tar.gz file into the myAmsTutorials directory.

**3.** Decompress the archive file:

```

gunzip AMSDInADE.tar.gz

tar xf AMSDInADE.tar

```

You are ready to begin.

The following tutorials are available at \$CDSHOME/tools/dfII/samples/tutorials/AMS/:

| File                                     | Documentation                                                                                                                                                |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AMSDInADE.tar.gz                         | "Building an AMS Test Case in ADE" on page 17                                                                                                                |  |

| MATLABCosimulation.tar.<br>gz            | Coming soon For now, see <i>Cosimulation Using the Virtuoso<sup>®</sup> AMS Designer Simulator and The MathWorks MATLAB<sup>®</sup>/Simulink<sup>®</sup></i> |  |

| AMSS_Envelope_ADE                        | Coming soon                                                                                                                                                  |  |

| AMSSpectreTurbo Coming soon              |                                                                                                                                                              |  |

| MigrateFromCBNToOSS<br>N.tar.gz          | "Migrating to the OSS Netlister" on page 129                                                                                                                 |  |

| MigrateFromVerimixToAM<br>SDinADE.tar.gz | "Migrating to AMS Designer" on page 69                                                                                                                       |  |

| MultiPowerDis.tar.gz                     | <u>"Using Digital Disciplines for Multiple Power Supply Design"</u> on page 157                                                                              |  |

| MultiPwerInhConn.tar.gz                  | <u>"Using Inherited Connections for Multiple Power Supply Design"</u><br>on page 137                                                                         |  |

# **Building an AMS Test Case in ADE**

You can take an existing schematic-based analog design and some digital (Verilog, in this example) text modules and build an AMS test case in the Virtuoso<sup>®</sup> Analog Design Environment (ADE) and run a full-chip AMS simulation.

**Note:** Begin this tutorial in the AMSDInADE subdirectory. This tutorial examples takes about 30 minutes to complete, not including the simulation run time for the design.

You can run the AMS Designer simulator from ADE or from the Virtuoso<sup>®</sup> Hierarchy Editor (HED). You can also run the AMS Designer simulator using a command-line interface. Being familiar with using other circuit simulators (such as Spectre, UltraSim, and SpectreVerilog) in ADE can help you understand this tutorial.

This tutorial demonstrates how you can build an AMS test case in ADE and HED. The basic steps are as follows:

- **1.** Start with an <u>existing analog schematic-based design</u> that you previously simulated using Spectre or UltraSim (or SpectreVerilog or UltraSimVerilog).

- 2. <u>Import the digital modules</u>—either Verilog or VHDL—into the Virtuoso design environment (we will demonstrate how to do this).

- 3. Complete the mixed-signal design in the Virtuoso Schematic Editor.

- 4. Configure the design in the Virtuoso Hierarchy Editor.

- 5. <u>Set up options and customize connect rules in ADE</u>.

- 6. Simulate the design using AMS in ADE.

/Important

Before starting this tutorial, see "Before You Begin" on page 13.

See the following topics for details:

- <u>The Tutorial Example</u> on page 19

- Using Verilog In to Import the Verilog Module into ADE on page 20

- <u>Viewing the Testbench for the PLL Design</u> on page 32

- Adding Divider Block Instances to the Tutorial Schematic on page 26

- Creating a Configuration View for AMS Simulation on page 34

- <u>Setting Up the Simulation in the Analog Design Environment</u> on page 39

- <u>Selecting Outputs for Plotting</u> on page 49

- <u>Creating and Displaying the Netlist</u> on page 53

- <u>Saving the State</u> on page 54

- Running the AMS Simulator with the Spectre Solver on page 55

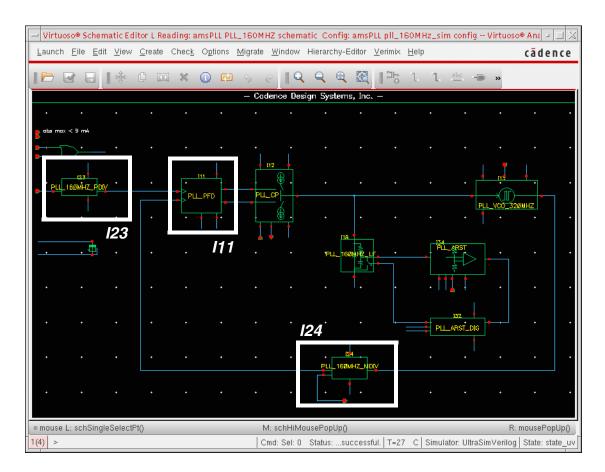

### **The Tutorial Example**

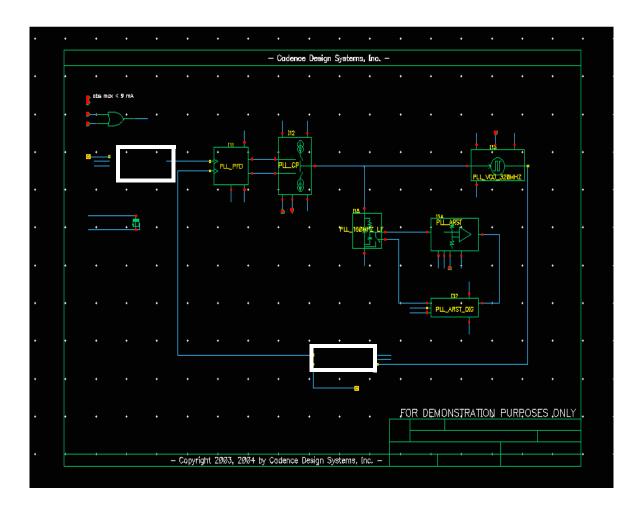

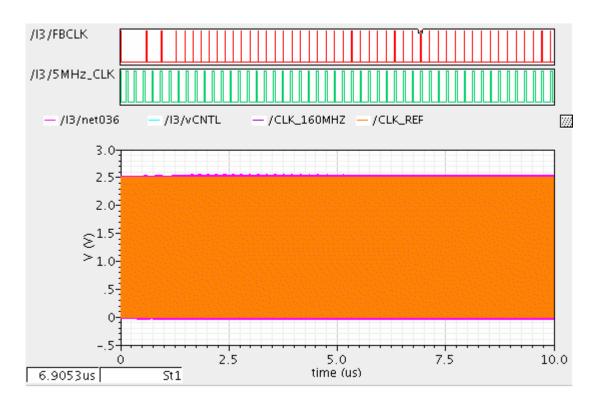

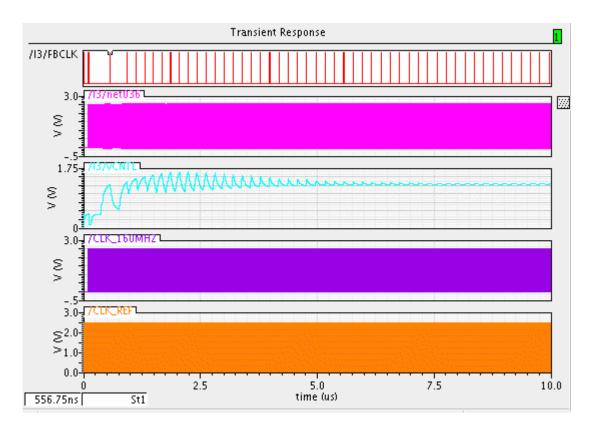

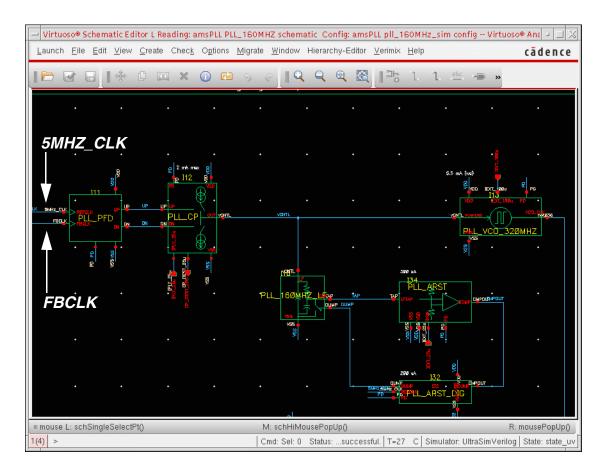

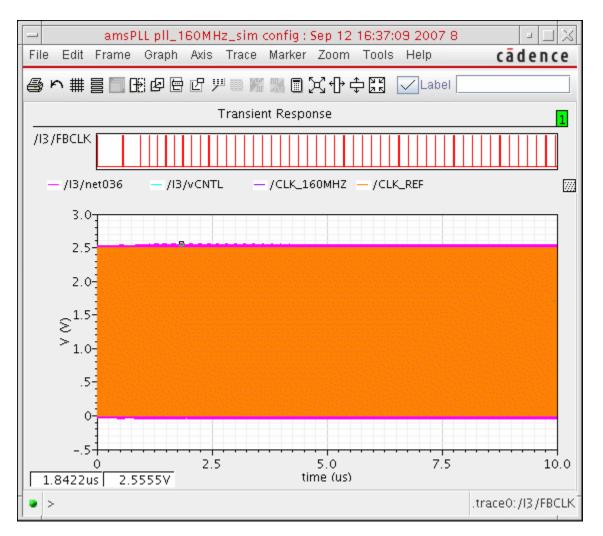

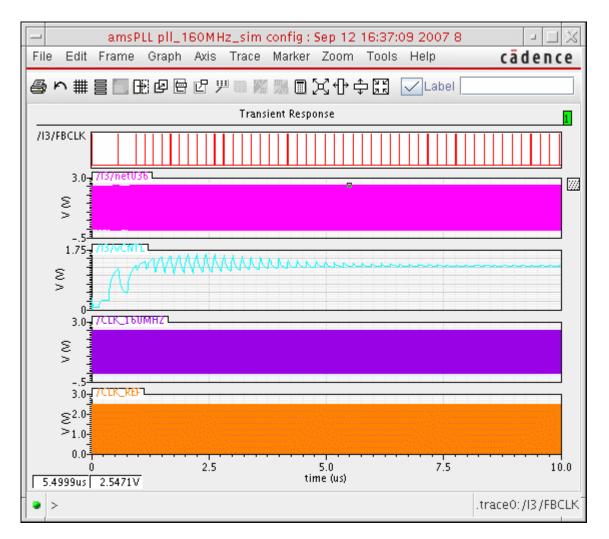

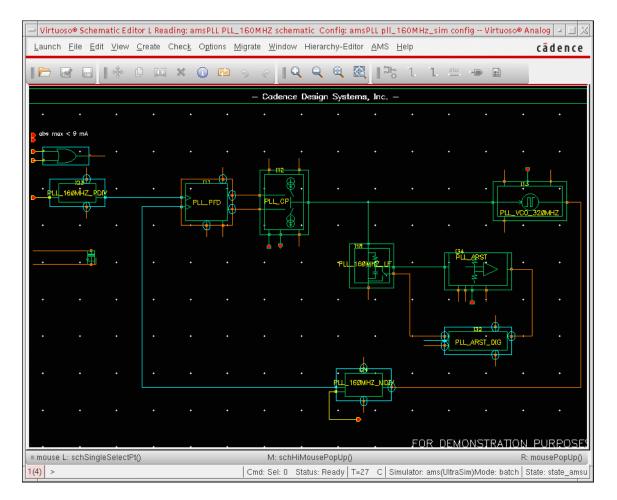

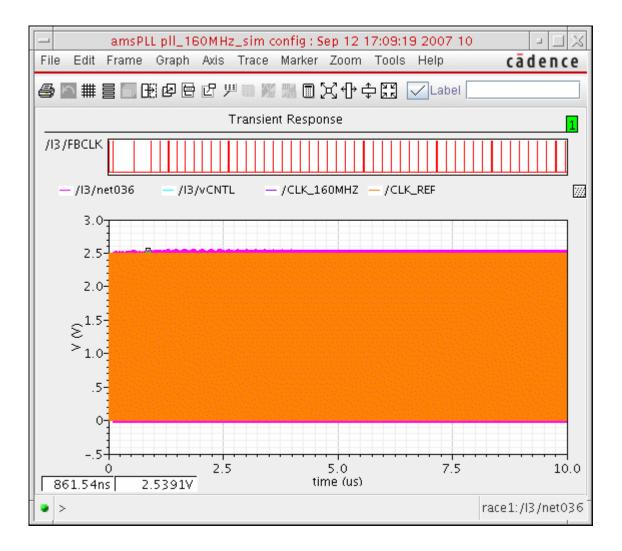

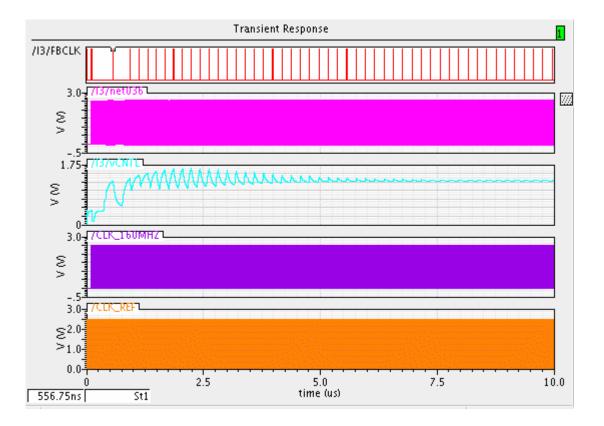

This tutorial example is a mixed-signal 160 MHz PLL circuit that consists of both schematic and Verilog language design units. The schematic contains the following analog components: a VCO, a phase frequency detector (PFD), a charge pump, and a loop filter. The two digital frequency dividers are RTL-level Verilog modules.

The key files and directories are:

| cds.lib       | Defines the associated libraries for designs, Cadence-shipped standard libraries, Fab foundry libraries, and so on |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|--|

| artist_states | Location of simulator setup information for ADE                                                                    |  |

| gpdk090       | 90nm process design kit (PDK)                                                                                      |  |

| models        | Device model files in Spectre format                                                                               |  |

| amsPLL        | Library of PLL blocks for the schematic database                                                                   |  |

| dig_source    | Location of the two behavioral Verilog frequency dividers                                                          |  |

| clean_up      | Script for cleaning up intermediate files                                                                          |  |

The key signals are:

| pll_160MHZ_sim.I3.vCNTL   | VCO's control voltage signal |

|---------------------------|------------------------------|

| pll_160MHZ_sim.CLK_REF    | 25 MHz clock reference       |

| pll_160MHZ_sim.CLK_160MHZ | 160 MHz PLL output           |

| pll_160MHZ_sim.I3.VCO_CLK | VCO's output voltage signal  |

## Using Verilog In to Import the Verilog Module into ADE

You can use <u>Verilog In</u> to import a Verilog<sup>®</sup> module into a Cadence library and create a symbol for that module for use in the Virtuoso<sup>®</sup> schematic editor. We will import the two Verilog behavioral frequency dividers from the dig\_source directory.

See the following topics for more information:

- Viewing the Verilog Behavioral Files for the Frequency Dividers on page 20

- Importing the Verilog Files into the Virtuoso Design Environment on page 21

- Viewing the New symbol and verilog Views for the Divider Cells on page 25

If you do not need to create a symbol for your module, you can use one of three other methods to import Verilog modules. See <u>"Importing Verilog Modules without Creating a Symbol"</u> on page 26 for more information.

### Viewing the Verilog Behavioral Files for the Frequency Dividers

To view the two Verilog behavioral frequency dividers in the dig\_source directory, do the following:

1. Change to the directory that contains the two behavioral Verilog frequency dividers:

cd dig\_source

**2.** Type ls to view the files:

ls

You will see the following two files:

| PLL_160MHZ_MDIV.v | Divider with factor 64, for VCO's output clock |

|-------------------|------------------------------------------------|

|                   |                                                |

- PLL\_160MHZ\_PDIV.v Divider with factor 5, for input reference clock

- **3.** Type more \*.v to view their contents.

#### Importing the Verilog Files into the Virtuoso Design Environment

To import these files into the Virtuoso design environment (that is, into the lib/cell/view structure of Cadence libraries), do the following:

**1.** Start Cadence software:

virtuoso &

**Note:** If you get a warning message such as the following in your CIW when you start Cadence software:

\*WARNING\* envLoadFile: file .cdsenv does not exist, or is not readable.

you can add ; ; to the beginning of the following command in the .cdsinit file so that it does not execute:

envLoadFile(".cdsenv")

2. In the CIW, choose File – Import – Verilog.

The Verilog In form appears.

| - Verilog In                                                      |                   |        |

|-------------------------------------------------------------------|-------------------|--------|

| Import Options Global Net Options Schematic Generation Options    |                   |        |

| File Filter Name                                                  |                   |        |

| /<br>amsPLL/<br>artist_states/<br>cds.lib<br>clean<br>dig_source/ |                   |        |

| /home/jillw/work/AMS                                              | G/IC612/amsdInGui |        |

| Target Library Name                                               |                   | Browse |

| Reference Libraries                                               | sample basic      |        |

| Verilog Files To Import                                           |                   | Add    |

| -f Options                                                        |                   | Add    |

| -v Options                                                        |                   | Add    |

| -y Options                                                        |                   | Add    |

| Library Extension                                                 |                   |        |

| Library Pre-Compilation                                           | n Options         |        |

| Pre Compiled Verilog Lib                                          | rary              |        |

| HDL View Name                                                     | hdl               |        |

3. In the Target Library Name field, type amsPLL.

| ,                   |        |        |

|---------------------|--------|--------|

| Target Library Name | amsPLL | Browse |

**Note:** You can also use the *Browse* button to open the Library Browser form and select *amsPLL* from the *Library* column on that form.

4. In the *File Filter Name* scrolling list box, double-click *dig\_source*.

The two Verilog behavioral files in that directory appear on the form.

|   | Import Options                          | Globa |

|---|-----------------------------------------|-------|

| 1 | File Filter Name                        |       |

|   | /<br>PLL_160MHZ_MDIY<br>PLL_160MHZ_PDIY |       |

- 5. For each of the two files in this list, do the following:

- **a.** Select the file name.

- **b.** To the right of the Verilog Files to Import field, click Add.

The full path to the file appears in the field. When more than one file name appears in the field, a space separates one file name from the next.

6. In the Structural View Names group box, type verilog in the Functional field.

| Structural View Names |           |         |         |  |

|-----------------------|-----------|---------|---------|--|

| Schematic             | schematic | Netlist | netlist |  |

| Functional            | verilog   | Symbol  | symbol  |  |

7. Select the *Global Net Options* tab.

|                         | Verilog In            | - <b>二</b> - 二 ス           |

|-------------------------|-----------------------|----------------------------|

| Import Options Gl       | obal Net Options Sc   | hematic Generation Options |

| Global Nets             |                       | ]                          |

| Power Net Name 🛛 🕅      | DD! Ground            | Net Name GND!              |

| Global Signals          |                       |                            |

| Net Expression          |                       |                            |

| Create Net Expression   |                       |                            |

| Net Expression Property | y Name for Power Net  | vdd                        |

| Net Expression Property | y Name for Ground Net | gnd                        |

|                         |                       |                            |

8. In the Power Net Name field, change VDD! to VDD1 !.

This tutorial example has nets VDD and VSS, and neither is a global net, so to avoid a name conflict (with our VDD net), we change the global power net name here to VDD1!.

**9.** Click *OK*.

Informational messages appear in the output area of the CIW.

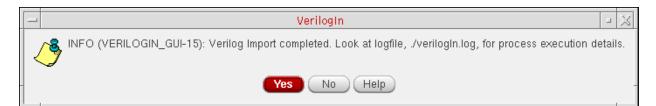

A prompt appears.

10. To view the log file, click Yes. (If you do not care to see the log file, you can click No.)

| - |              | Log File 🗳 🛄                                                                          | $\mathbb{X}$ |

|---|--------------|---------------------------------------------------------------------------------------|--------------|

|   | <u>F</u> ile | Help cādence                                                                          | 9            |

| F | @(#)\$       | CDS: ihdl.exe version 6.1.2 08/21/2007 14:32 (cic612lnx) \$ Wed Aug 22 10:40:46 2007  |              |

| l | INFO         | (VERILOGIN-357): Checked in symbol PLL_160MHZ_MDIV.                                   |              |

| l | INFO         | (VERILOGIN-345): Checked in functional view PLL_160MHZ_MDIV. Expression on port found |              |

| l | INFO         | (VERILOGIN-357): Checked in symbol PLL_160MHZ_PDIV.                                   |              |

| l | INFO         | (VERILOGIN-345): Checked in functional view PLL_160MHZ_PDIV. Expression on port found |              |

| l | INFO         | (VERILOGIN-206): End of Logfile.                                                      |              |

|   | 2<br>2       |                                                                                       | -            |

11. Choose File – Close Window to close the log file viewing window.

#### Viewing the New symbol and verilog Views for the Divider Cells

You can view the new symbol and verilog views for these two new cells (PLL\_160MHZ\_MDIV and PLL\_160MHZ\_PDIV) in the amsPLL library as follows:

- **1.** In the CIW, choose *Tools Library Manager*.

- 2. In the *Library* column, select *amsPLL*.

- **3.** In the *Cell* column for each new cell, select the new cell name (*PLL\_160MHZ\_MDIV* and *PLL\_160MHZ\_PDIV*).

In the View column for each new cell you select, both symbol and verilog views appear.

| 🖃 Library Manager: Directorystcases/shweta/myAMS/AMSDInADE 💿 📃 刘 |                                           |                   |            |

|------------------------------------------------------------------|-------------------------------------------|-------------------|------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>D</u> esign Manager    | <u>H</u> elp                              |                   | cādence    |

| 🔲 Show Categories 📃 Show                                         | ' Files                                   | _                 |            |

| Library                                                          | Cell                                      | ~View             |            |

| amsPLL                                                           | PLL_160MHZ_MDIV                           |                   |            |

| aExamples                                                        | PLL_160MHZ<br>PLL_160MHZ_LF               | View 🔺            | Lock Size  |

| amsPLL<br>analogLib                                              | PLL_160MHZ_LF                             | symbol<br>verilog | 25k<br>538 |

| basic<br>cdsDefTechLib                                           | PLL_160MHZ_MDIV_answer<br>PLL_160MHZ_PDIV | Ŭ                 |            |

| connectLib                                                       | PLL_160MHZ_PDIV_answer                    |                   |            |

| gpdk090<br>sample                                                | PLL_160MHZ_answer<br>PLL_160MHZ_sim       |                   |            |

|                                                                  |                                           | p                 |            |

| Messages                                                         |                                           |                   |            |

| Log file is "/net/cicsol20d/export/ho                            | me/selvats/cic/testcases/shweta/myAN      | /IS/AMSDI         |            |

|                                                                  |                                           |                   |            |

|                                                                  |                                           |                   |            |

| -                                                                |                                           |                   |            |

**Note:** You can ignore the *PLL\_160MHZ\_MDIV\_answer* and *PLL\_160MHZ\_PDIV\_answer* cells which we provided with this tutorial for your reference and convenience only.

### Importing Verilog Modules without Creating a Symbol

You can use the following methods to import a Verilog module for simulation:

• Use -y/-v in the analog design environment (ADE) to specify the Verilog text module.

**Note:** This method produces results similar to the original SpectreVerilog simulator. For information about how to specify these options, see <u>"Specifying Library Files and Directories for the Compiler"</u> in the *Virtuoso AMS Designer Environment User Guide*. See also <u>"Choose Simulation – Options – AMS Simulator"</u> in the "Running a Simulation" chapter of the *Virtuoso Analog Design Environment L User Guide*.

- <u>Specify the Verilog source file</u> in the Virtuoso<sup>®</sup> hierarchy editor.

- Use ncvlog -use5x to compile the Verilog module into a lib/cell/view Cadence library structure.

See "novlog Command Syntax and Options" in the *Virtuoso AMS Designer Simulator* User Guide for information about the -use5x option.

When you use any of these methods, you must create the symbol yourself. Alternatively, you can use Verilog In to create a symbol for you. See <u>"Using Verilog In to Import the Verilog</u> <u>Module into ADE</u>" on page 20 for more information.

### **Adding Divider Block Instances to the Tutorial Schematic**

To add component instances for the Verilog behavioral divider cells to the tutorial schematic, do the following:

**1.** In the Library Manager, select *amsPLL*, *PLL\_160MHZ*, *schematic*.

| Library Manager: Di                                                                           | rectorystcases/shweta/myAMS/AN                                                                                                                               | 1SDInADE                                                | X L L                               |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>D</u> esign Manager                                 | ' <u>H</u> elp                                                                                                                                               |                                                         | cādence                             |

| 🔄 Show Categories 🔛 Shov                                                                      | v Files<br>V <b>Cell</b>                                                                                                                                     | - View                                                  |                                     |

| amsPLL                                                                                        | PLL_160MHZ                                                                                                                                                   | schematic                                               |                                     |

| aExamples<br>amsPLL<br>analogLib<br>basic<br>cdsDefTechLib<br>connectLib<br>gpdk090<br>sample | PLL_160MHZ<br>PLL_160MHZ_LF<br>PLL_160MHZ_MDIV<br>PLL_160MHZ_MDIV_answer<br>PLL_160MHZ_PDIV<br>PLL_160MHZ_PDIV_answer<br>PLL_160MHZ_answer<br>PLL_160MHZ_sim | View<br>behavioral<br>schematic<br>symbol<br>verilogams | Lock Size<br>2k<br>39k<br>27k<br>2k |

| Messages                                                                                      | ome/selvats/cic/testcases/shweta/myAl                                                                                                                        | MS/AMSD                                                 |                                     |

|                                                                                               |                                                                                                                                                              |                                                         |                                     |

2. Choose File – Open.

The tutorial schematic appears in a Schematic Editor window. There are vacancies on the schematic where you will place the new symbols.

**3.** Place an instance of *PLL\_160MHZ\_PDIV* in the upper left vacancy and connect the nets as follows:

-↓ Tip

If you want instructions for how to select and place these parts on the schematic, see <u>"Selecting and Placing Divider Cell Instances"</u> on page 31.

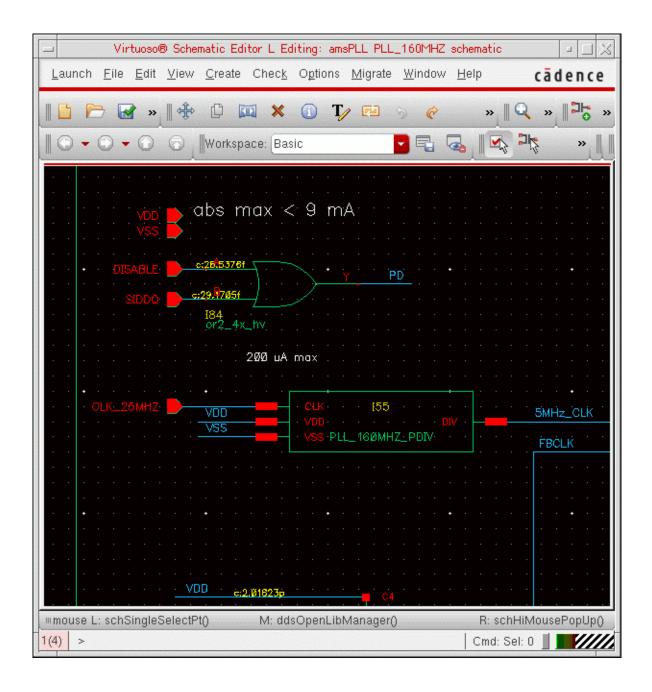

**4.** Place an instance of *PLL\_160MHZ\_MDIV* in the lower vacancy and connect the nets as follows:

| L Vir                       | rtuoso® Schematic Editor L Editing: amsPLL PLL_160MHZ schematic                                                     | >                                          |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| <u>L</u> aunch <u>F</u> ile | <u>E</u> dit <u>V</u> iew <u>C</u> reate Chec <u>k</u> O <u>p</u> tions <u>M</u> igrate <u>W</u> indow <u>H</u> elp | cādence                                    |

| II 🗈 🗁 🖪                    | 🖌 » 🛚 💠 🗘 🖾 🗶 🛈 T⁄y 🖼 5 🥜 🛛 » 🛛                                                                                     | Q »∥₽ <mark>;</mark> ,                     |

| 0.0.                        | 🗸 🕥 🕞 Workspace: Basic                                                                                              | ₽ <b> </b> 5                               |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             | - · · · · · · · · · · · · · · · · · · ·                                                                             | VSS                                        |

|                             |                                                                                                                     | VDD                                        |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             |                                                                                                                     |                                            |

|                             | └──── <b>─</b> ───────────────────────────────                                                                      |                                            |

|                             |                                                                                                                     |                                            |

| mouse L: sch                | SingleSelectPt() M: ddsOpenLibManager() R: schl                                                                     | HiMousePopUp()                             |

| (4) >                       | Cmd: Se                                                                                                             | a contra pro transmissione a contra sector |

**Note:** Remember to type *r* twice to rotate the part to its correct orientation.

5. Check and save the schematic.

Note: We provided the <code>PLL\_160MHZ\_answer</code> schematic with this tutorial for your reference and convenience.

#### **Selecting and Placing Divider Cell Instances**

To select and place divider cell instances, do the following:

1. In the schematic editor, choose *Create – Instance* (or type i).

The Add Instance form appears.

2. Click Browse.

The Library Browser window appears.

- 3. In the *Library* column, select *amsPLL*.

- 4. Click Filters.

The View Filter By form appears.

**5.** In the *Cell Filter* field, type PLL\_160MHZ\* to narrow the search field and click *OK*.

Only cell names beginning with this string appear in the Cell column.

6. In the Library Browser window, select PLL\_160MHZ\_PDIV.

As you drag your mouse over the schematic, you can see the outline of the symbol.

- 7. Click to place the instance on the schematic.

- 8. Select PLL\_160MHZ\_MDIV.

As you drag your mouse over the schematic, you can see the outline of the symbol. You will need to change the orientation of this instance before placing it.

- **9.** Type r twice to rotate the instance into the correct orientation.

- **10.** Click to place the instance on the schematic.

- **11.** Press *Esc* when finished.

For more information, see "Adding Instances" in the <u>"Creating Schematics"</u> chapter of the *Virtuoso Schematic Editor L User Guide*.

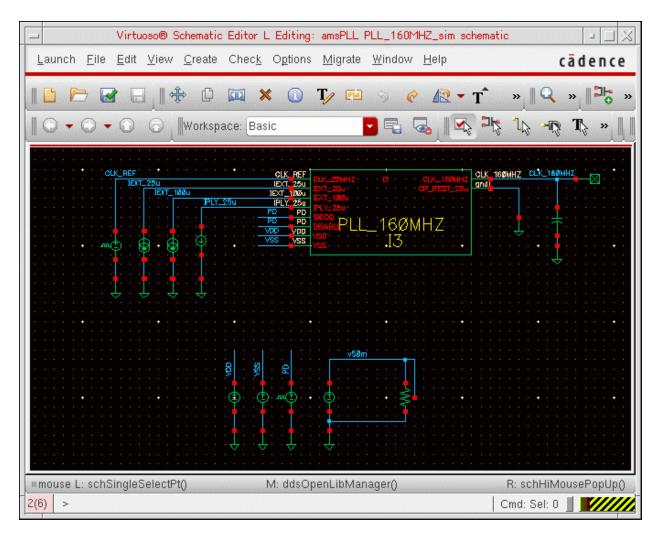

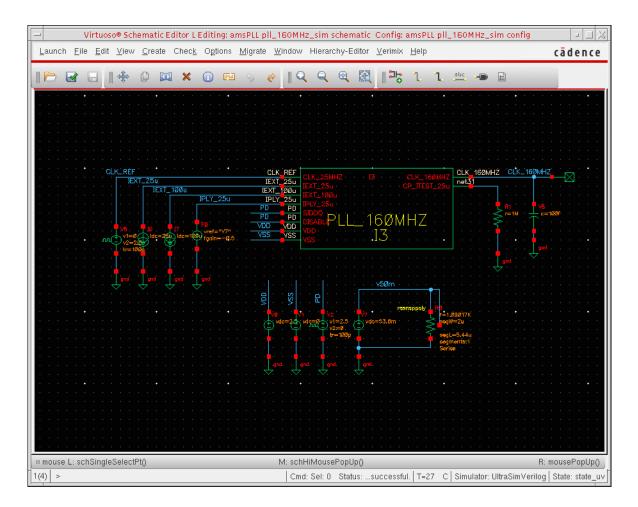

### Viewing the Testbench for the PLL Design

To view the testbench schematic for the tutorial example (a PLL design), do the following:

**1.** In the Library Manager, select *amsPLL*, *pll\_160MHZ\_sim*, *schematic*.

| 🖃 📃 Library Manager: Directoryjillw/work/AMS/IC612/amsdInGui 🛛 📮 🗔 🔀             |                                                                                                   |           |         |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------|---------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>D</u> esign Mana,                      | ger <u>H</u> elp                                                                                  |           | cādence |

| 🔲 Show Categories 📃 S                                                            | how Files                                                                                         |           |         |

| Library                                                                          | Cell                                                                                              | View      | ]       |

| amsPLL                                                                           | pll_160MHZ_sim                                                                                    | schematic |         |

| amsPLL<br>analogLib<br>basic<br>cdsDefTechLib<br>connectLib<br>gpdk090<br>sample | pll_160MHZ_sim<br>sheet_a<br>sheet_aa<br>sheet_b<br>sheet_c<br>tiehi_hv<br>tielo_hv<br>vor2_1x_bu | schematic |         |

| - Messages                                                                       |                                                                                                   |           |         |

| Log file is "/home/jillw/work/AMS                                                | /IC612/amsdInGui/libManager.log".                                                                 |           |         |

|                                                                                  |                                                                                                   |           | . 1.    |

2. Choose File - Open.

The testbench schematic appears in a Schematic Editor window.

Notice that the power supply (*VDD*) is 2.5 Volts.

# **Creating a Configuration View for AMS Simulation**

To create a configuration view for the testbench schematic for AMS simulation, do the following:

1. In the Library Manager, select *amsPLL*, *pll\_160MHZ\_sim*.

| 🗕 Library Manager: Directoryjillw/work/AMS/IC612/amsdInGui 💷 🗔 🔀                 |                                                                                                                     |               |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>D</u> esign Mana                       | ager <u>H</u> elp                                                                                                   | c ā d e n c e |

| ☐ Show Categories ☐ S                                                            | Show Files                                                                                                          | View          |

| amsPLL<br>analogLib<br>basic<br>cdsDefTechLib<br>connectLib<br>gpdk090<br>sample | pll_160MHZ_sim<br>pll_160MHZ_sim<br>sheet_a<br>sheet_aa<br>sheet_b<br>sheet_c<br>tiehi_hv<br>tielo_hv<br>vor2_1x_hu | schematic     |

| Messages                                                                         | 5/IC612/amsdInGui/libManager.log".                                                                                  |               |

2. Choose File - New - Cell View.

The New File form appears.

#### **3.** In the *Type* field, select *config*.

| -                                                 | New File 🖃 🗔 🔀     |  |  |  |

|---------------------------------------------------|--------------------|--|--|--|

| File                                              |                    |  |  |  |

| Library                                           | amsPLL             |  |  |  |

| Cell                                              | pll_160MHZ_sim     |  |  |  |

| View                                              | config             |  |  |  |

| Туре                                              | config 🔽           |  |  |  |

| Application —                                     |                    |  |  |  |

| Open with                                         | Hierarchy Editor 🔽 |  |  |  |

| Always use this application for this type of file |                    |  |  |  |

| Library path file                                 |                    |  |  |  |

| me/jillw/work/AMS/IC612/amsdInGui/cds.lib         |                    |  |  |  |

|                                                   |                    |  |  |  |

|                                                   |                    |  |  |  |

|                                                   | OK Cancel Help     |  |  |  |

4. Click OK.

The New Configuration form appears.

5. In the *View* field in the *Top Cell* group box, select *schematic*.

| - |              | New Configuration                       |   | 5 |

|---|--------------|-----------------------------------------|---|---|

|   | ∼Top Cell−   |                                         |   |   |

|   |              |                                         |   |   |

|   | Library:     | amsPLL                                  |   |   |

|   | Cell:        | pll_160MHZ_sim                          |   |   |

|   | View:        | schematic                               |   |   |

|   | Clobal Div   | dinac                                   |   |   |

|   | – Global Bin |                                         |   |   |

|   | Library Lis  | st:                                     |   |   |

|   | View List:   |                                         |   |   |

|   | Stop List:   |                                         |   |   |

|   | Constraint   | : List:                                 |   |   |

|   | Descriptio   | )n ———————————————————————————————————— | _ |   |

|   |              |                                         | - |   |

|   |              |                                         |   |   |

|   |              |                                         |   |   |

|   |              |                                         |   |   |

|   |              |                                         |   |   |

|   |              |                                         |   |   |

|   | (            |                                         |   |   |

|   |              | OK Cancel Use Template Help             |   |   |

| - |              | Cancel Ose reinplate (help)             |   | - |

|   |              |                                         |   |   |

6. Click Use Template.

7. In the *Name* field in the *Template* group box, select *AMS*.

| - | 1            | Use Template 🕘 📃        | 1 X |

|---|--------------|-------------------------|-----|

| L | - Template - |                         | ה   |

|   | Name:        | <other></other>         |     |

|   | From File:   | <other><br/>AMS</other> |     |

| 1 |              | AMS_Compatibility       | ΡI  |

|   |              | auLvs<br>hspiceD        |     |

|   |              | spectre                 |     |

|   |              | spectreVerilog          | -   |

|   | 1            | verilog<br>vhdlinteg    |     |

8. On the Use Template form, click OK.

Bindings appropriate for AMS simulation appear in the fields of the *Global Bindings* group box. For more information about global bindings, see "Global Bindings Section" in the <u>"Cadence Hierarchy Editor Overview."</u>

|   |                                                                                                                                                                                                                           | New Configuration                                     |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

|   | - Top Cell                                                                                                                                                                                                                |                                                       |  |

|   | Library: ams                                                                                                                                                                                                              | PLL                                                   |  |

|   | Cell: PLL                                                                                                                                                                                                                 | _160MHZ_sim                                           |  |

|   | View: sch                                                                                                                                                                                                                 | ematic                                                |  |

|   | Global Binding                                                                                                                                                                                                            | \$                                                    |  |

|   | Library List:                                                                                                                                                                                                             | basic analogLib                                       |  |

|   | View List:                                                                                                                                                                                                                | atic verilogams veriloga behavioral functional symbol |  |

|   | Stop List:                                                                                                                                                                                                                | symbol                                                |  |

|   | Constraint List:                                                                                                                                                                                                          |                                                       |  |

|   | - Description                                                                                                                                                                                                             |                                                       |  |

|   | Default config view template for OSS-based and Cellview-based Veri<br>AMS netlisters in ADE.<br>Note:<br>Please remember to replace Top Cell Library, Cell, and View<br>fields with the actual names used by your design. |                                                       |  |

| - |                                                                                                                                                                                                                           | OK Cancel Use Template Help                           |  |

In this tutorial design, most cells are schematic cells. Only <code>PLL\_160MHZ\_MDIV</code> and <code>PLL\_160MHZ\_PDIV</code> are Verilog cells. Therefore, to get the cell bindings you want, you need to change the view list so that <code>verilog</code> and <code>schematic</code> appear at the beginning of the list.

**9.** In the *View List*, click to place the edit cursor and change the view list so that verilog and schematic appear at the beginning of the list.

verilog schematic ...

- **10.** Click *OK*.

- **11.** In the Virtuoso<sup>®</sup> Hierarchy Editor window, choose File Save (Needed).

The config view is open in the hierarchy editor and the schematic view is open in the schematic editor.

## Setting Up the Simulation in the Analog Design Environment

To set up the simulation in the analog design environment (ADE), do the following:

- Launching ADE on page 39

- Selecting the AMS Designer Simulator with the Spectre Solver on page 41

- <u>Specifying the Transient Analysis</u> on page 42

- <u>Specifying the Model Libraries</u> on page 43

- Customizing Connect Rules on page 45

#### Launching ADE

To launch ADE and specify the config view, do the following:

**1.** In the Schematic Editor window for *amsPLL pll\_160MHZ\_sim schematic*, choose *Launch – ADE L*.

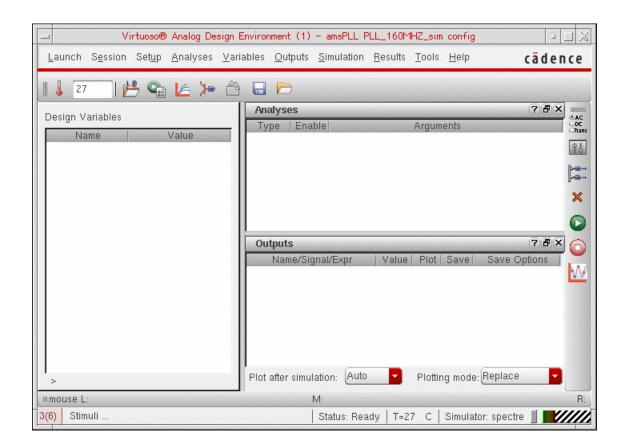

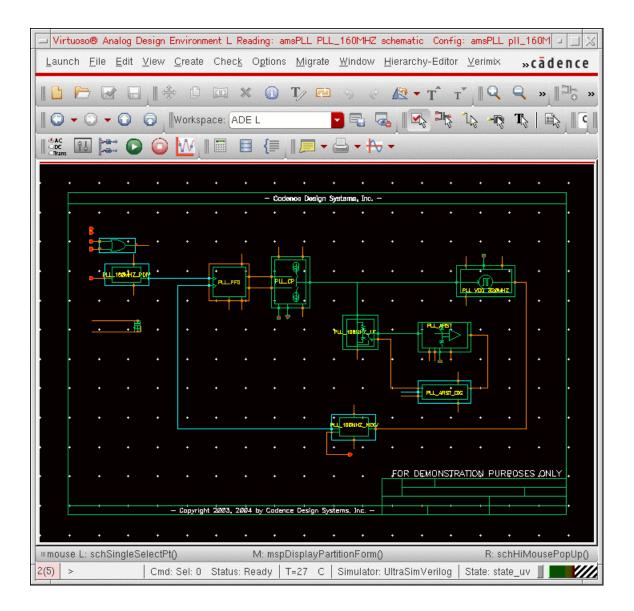

| Uirtuoso® Analog Desig                                                   | n Environment (1) - amsPLL PLL_160MHZ_sim config 🛛 🖓 🖂 🔀                                                                   |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| <u>L</u> aunch S <u>e</u> ssion Set <u>u</u> p <u>A</u> nalyses <u>v</u> | ariables <u>Outputs</u> <u>Simulation</u> <u>Results</u> <u>Tools</u> <u>H</u> elp <b>cādence</b>                          |

| 🌡 27 🛛 💾 💁 🖆 🎾 (                                                         | 🖄 🖬 🏷                                                                                                                      |

| Design Variables                                                         | Analyses ?                                                                                                                 |

| Name Value                                                               | 21<br>22<br>23<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24                               |

|                                                                          | Outputs       Image: Save Options         Name/Signal/Expr       Value       Plot       Save       Save Options            |

| ><br>#mouse L:<br>8(16) Stimuli                                          | Plot after simulation: Auto Plotting mode: Replace<br>M: R:<br>Status: Ready   T=27 C   Simulator: ams(Spectre)Mode: batch |

The Virtuoso<sup>®</sup> Analog Design Environment window appears.

In order to select the AMS simulator in ADE, you must choose the config view first.

**2.** Choose *Setup – Design*.

The Choosing Design form appears.

3. In the View Name field, select config.

| [ | L Choosing   | Design Virtuoso® Analog Design Environment (1) 🏻 🖃 🔀                                                                                                                       |

|---|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Library Name | amsPLL                                                                                                                                                                     |

|   | Cell Name    | PLL_160MHZ_PDIV<br>PLL_160MHZ_PDIV_answer<br>PLL_160MHZ_answer<br>PLL_160MHZ_sim<br>PLL_ARST<br>PLL_ARST<br>PLL_ARST_DIG<br>PLL_CP<br>PLL_INV10X<br>PLL_INV3X<br>PLL_INV3X |

|   | View Name    | config                                                                                                                                                                     |

|   | Open Mode    | 🖲 edit 🥥 read                                                                                                                                                              |

|   |              | OK Cancel Help                                                                                                                                                             |

4. Click OK.

config appears in the title banner of the ADE window.

| _                  | V              | irtuoso® Ai      | nalog Desig       | jn Enviro       | nment (1) -        | amsPLL          | pll_160       | MHZ_sim      | config |   |

|--------------------|----------------|------------------|-------------------|-----------------|--------------------|-----------------|---------------|--------------|--------|---|

| S <u>e</u> ssion : | Set <u>u</u> p | <u>A</u> nalyses | <u>V</u> ariables | <u>O</u> utputs | <u>S</u> imulation | <u>R</u> esults | <u>T</u> ools | <u>H</u> elp |        | ( |

Now you can select the AMS simulator.

#### Selecting the AMS Designer Simulator with the Spectre Solver

To select the AMS Designer simulator with the Spectre solver, do the following:

**1.** Choose *Setup – Simulator/Directory/Host*.

The Choosing Simulator form appears.

2. In the *Simulator* field, select *ams*.

|   | _   | Choosing Simula | ator/Directory/Hos                       | t Virtuoso® Analog Design Envirc 🍙 🗔 | $\mathbb{X}$ |

|---|-----|-----------------|------------------------------------------|--------------------------------------|--------------|

|   | Sir | nulator         | spectre                                  |                                      |              |

|   | Pro | oject Directory | hspiceD<br>spectre<br>UltraSim           |                                      |              |

| l | Ho  | ist Mode        |                                          | 💛 distributed                        |              |

|   | Ho  | ost             | ams<br>spectreVerilog<br>UltraSimVerilog |                                      |              |

|   | Re  | mote Directory  |                                          |                                      | )            |

|   |     |                 |                                          | K Cancel Defaults Apply Hel          | 0            |

3. Click OK.

*ams* appears in the window header after *Simulator*. The currently configured analog solver appears next to *ams* in parentheses. *Spectre* is the default analog solver. We will use the Spectre solver for this part of the tutorial.

| 8(16) | Simulator/Directory/Host | Status: Ready | T=27 | С | Simulator: ams(Spectre) | /lode: batch |  |

|-------|--------------------------|---------------|------|---|-------------------------|--------------|--|

|       | · ·                      | 1 /           | 1    |   |                         |              |  |

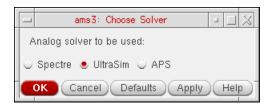

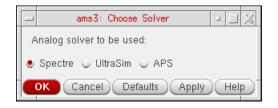

**Note:** You can change the solver on the Choose Solver form by choosing *Simulation – Solver*.

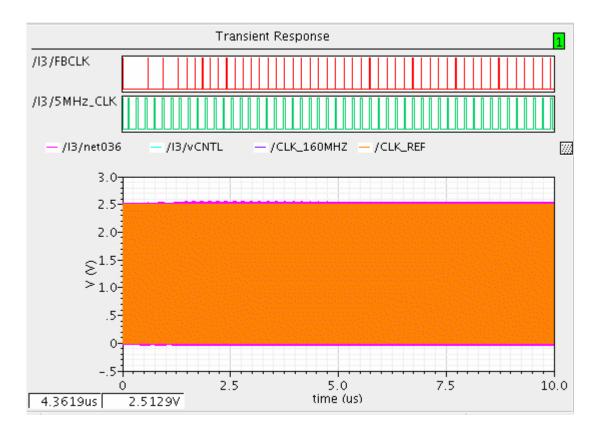

#### **Specifying the Transient Analysis**

To specify the transient analysis for this tutorial, do the following:

**1.** Choose Analyses – Choose.

The Choosing Analyses form appears. The default Analysis selection is tran.

2. In the Stop Time field, type 8u.

A check mark appears in the *Enabled* check box.

| - Choosing Analyses Virtuoso® Analog Design Environ 🖃 🗔 🔀 |

|-----------------------------------------------------------|

| Analysis 💩 tran 🤤 dc 🤤 ac 🤤 envlp                         |

| Transient Analysis                                        |

| Stop Time 8ul                                             |

| Accuracy Defaults (errpreset - Spectre Only)              |

| 🔲 conservative 🔲 moderate 🔛 liberal                       |

| Transient Noise                                           |

| Enabled 👱 Options                                         |

| OK Cancel Defaults Apply Help                             |

**3.** Click *OK*.

The transient analysis setup appears in the Analyses area in the ADE window.

| Analyses |          |           |  |

|----------|----------|-----------|--|

| _ Туре 🗸 | Enable   | Arguments |  |

| 1 tran   | <b>V</b> | 0 8u      |  |

### Specifying the Model Libraries

To specify the model libraries for this tutorial, do the following:

**1.** Choose Setup – Model Libraries.

The Model Library Setup form appears.

| [ | ams2: Model Library Setup                                                         |                 | - U X |               |

|---|-----------------------------------------------------------------------------------|-----------------|-------|---------------|

|   | ┢- Global Model File<br>└── <click add="" file="" here="" model="" to=""></click> | Section         | * *   | Browse button |

|   |                                                                                   | OK Cancel Apply | Help  |               |

- **2.** Click the browse button.

- **3.** On the Choose form that appears, navigate to and double-click models/spectre/gpdk090.scs.

- **4.** To select a particular section, click once in the Section column so that the down arrow appears.

| - | ams2: Model Library Setup                                                                                     |            |

|---|---------------------------------------------------------------------------------------------------------------|------------|

|   | Model File Section<br>Global Model Files<br>✓ /home/jillw/work/AMS/IC612/amsdlnGui/models/spectre/gpdk090.scs | Down arrov |

|   | OK Cancel App                                                                                                 | ply Help   |

5. On the drop-down list that appears in the *Section* column, select *NN*.

|    | Section |  |

|----|---------|--|

| [  |         |  |

| NN |         |  |

| SS |         |  |

| SF |         |  |

| FS |         |  |

| FF |         |  |

6. On the Model Library Setup form, click OK.

#### **Customizing Connect Rules**

The power supply for the PLL design in this tutorial is 2.5 Volts. There are no built-in rules for this voltage, so you need to customize a set of connect rules for 2.5 Volts. We will select and customize the connect rules for a 3-Volt supply.

To customize connect rules for this tutorial, do the following:

**1.** In the Virtuoso<sup>®</sup> Analog Design Environment window, choose *Setup – Connect Rules*.

The Select Connect Rules form appears. *ConnRules\_5V\_full* appears in the *List of Connect Rules Used in Simulation* table by default.

**2.** Select *ConnRules\_5V\_full* and click *Delete*.

|   |    | ams3: Select Connect Rules 💷 📃                               | 2 |  |  |  |  |  |

|---|----|--------------------------------------------------------------|---|--|--|--|--|--|

|   | Li | List of Connect Rules Used in Simulation                     |   |  |  |  |  |  |

| l |    | Type Rule Name Details                                       | [ |  |  |  |  |  |

| l |    | Built-in ConnRules_18V_full_fast Lib:connectLib View:connect |   |  |  |  |  |  |

|   |    |                                                              |   |  |  |  |  |  |

| l |    |                                                              |   |  |  |  |  |  |

|   | (  | Enable Disable Delete Rename Copy Up Down Customize          |   |  |  |  |  |  |

This action removes the default connect rules so that you can specify your own set of customized connect rules for this tutorial.

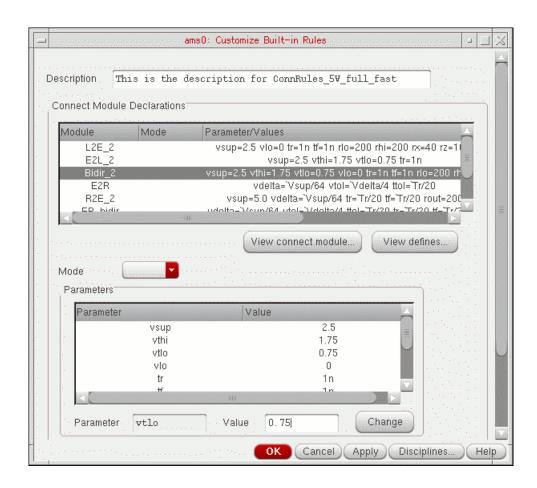

**3.** Using the drop-down combo box in the *Rules Name* field of the *Built-in rules* group box, select *connectLib.ConnRules\_18V\_full\_fast*.

The  $_full$  rules are the most accurate. Cadence recommends the  $_full_fast$  rules for use with AMS Designer. You can customize the built-in rules you select for the supply value of your design. In this case, the PLL is a 2.5-Volt design.

4. Click *Customize*.

#### The Customize Built-in Rules form appears.

| Module                                                | Mode Parameter/Values                                                                                                                                                                                                        |                                                                                 |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| L2E_2<br>E2L_2<br>Bidir_2<br>E2R<br>R2E_2<br>EB_bidir | vsup=3.0 vlo=0 tr=0.4n tf=0.4n rlo=200<br>vsup=3.0 vthi=2.0 vtlo=1<br>vsup=3.0 vthi=2.0 vtlo=1.0 vlo=0 tr=0.<br>vdelta=`Vsup/64 vtol=`Vdelta<br>vsup=3.0 vdelta=`Vsup/64 tr=Tr/2<br>vdelta=`)(cup/64 vtol=`)(delta/4 ttol=Tr | 1.0 tr=0.4n<br>4n tf=0.4n rlo=200 i<br>a/4 ttol=`Tr/20<br>:0 tf=`Tr/20 rout=200 |

| Mode                                                  |                                                                                                                                                                                                                              |                                                                                 |

| Mode<br>Parameters                                    | Value                                                                                                                                                                                                                        |                                                                                 |

| Parameters                                            | Value                                                                                                                                                                                                                        |                                                                                 |

| Parameters                                            |                                                                                                                                                                                                                              | hange                                                                           |

| Parameters                                            |                                                                                                                                                                                                                              | hange                                                                           |

5. In the Description field, click to place the edit cursor and change the description to

This is the description for My\_ConnRules\_25V\_full\_fast

Description This is the description for My\_ConnRules\_25V\_full\_fast

6. In the *Connect Module Declarations* table, highlight the top three lines containing information for modules *E2L\_2*, *L2E\_2*, and *Bidir\_2*.

The parameters for these modules appear in the *Parameters* group box.

|                                           | ams3: Customi                         | ize Built-in Rules                       |                                                                                                     | L   ×                        |

|-------------------------------------------|---------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------|

| Description This                          | is the description                    | n for My_ConnRule                        | es_25V_full_fast                                                                                    |                              |

| Module                                    | Mode Paramet                          | er/Values                                |                                                                                                     |                              |

| L2E_2<br>E2L_2<br>Bidir 2<br>E2R<br>R2E_2 | vsup=3.<br>vsu                        | .0 vthi=2.0 vtlo=1.0 v                   | -2.0 vtlo=1.0 tr=0.4n<br>lo=0 tr=0.4n tf=0.4n<br>vtol=`Vdelta/4 ttol=`Tr.<br>64 tr=`Tr/20 tf=`Tr/20 | rio=200 i<br>/20<br>rout=200 |

| Mode                                      |                                       | View connect mod                         | View def                                                                                            | īnes                         |

| Parameter                                 | Vsup<br>Vlo<br>tr<br>tf<br>rlo<br>rbi | Value<br>3.0<br>0.4<br>0.4<br>200<br>200 | n<br>n<br>0                                                                                         |                              |

| Parameter                                 |                                       | ie                                       | Change                                                                                              |                              |

| Direction1                                |                                       | scipline1                                |                                                                                                     |                              |

| Connect Resolution                        | 16                                    | OK Cancel                                | Apply Disciplir                                                                                     | nes) (Help                   |

7. Change these values as follows:

| Parameter | Value | Change it to |

|-----------|-------|--------------|

| vsup      | 1.8   | 2.5          |

| vthi      | 1.2   | 1.7          |

| vtlo      | 0.6   | 0.8          |

a. Select the parameter you want to change.

Note: For vthi and vtlo, use the scroll bar to scroll down to the bottom of the list.

Its name appears in the Parameter field. Its value appears in the Value field.

- **b.** In the Value field, click and drag the mouse to highlight the value for editing.

- c. Type the new value.

- d. Click Change.

- 8. Click *OK*.

An Information prompt appears.

| - | -    |           | ams2: Inf      | orm | ation                        |       |      |

|---|------|-----------|----------------|-----|------------------------------|-------|------|

|   | used | for si    |                |     | le to the l:<br>k on Add but |       |      |

|   | Do n | ot show t | his dialog aga | in  |                              |       |      |

|   |      |           |                |     | ОК                           | ancel | Help |

- 9. Click *OK* on the Information prompt.

- 10. On the Select Connect Rules form, click Add.

Modified built-in appears in the Type column.

**11.** Select the *Modified built-in* rule and click *Rename*.

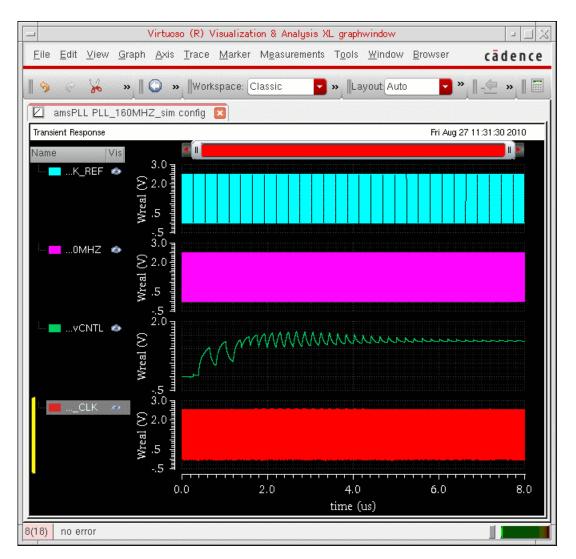

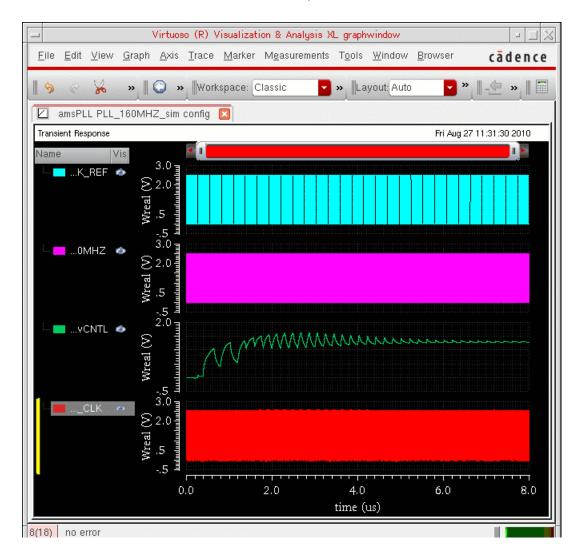

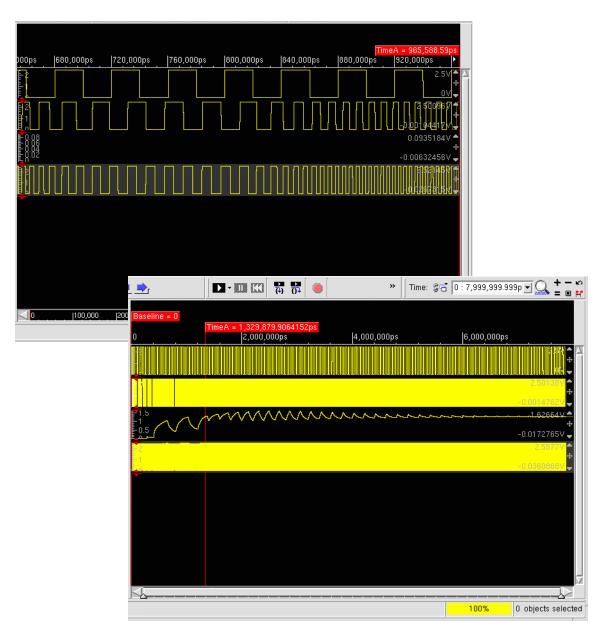

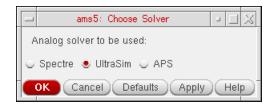

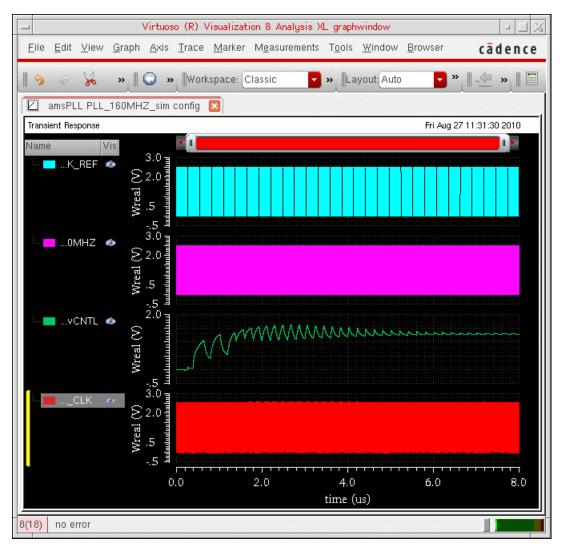

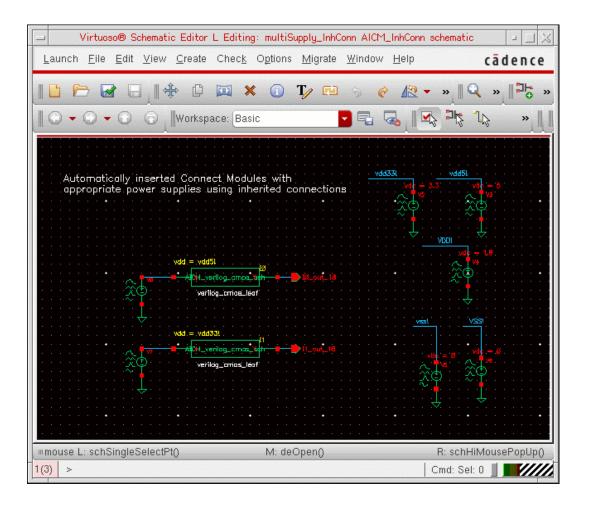

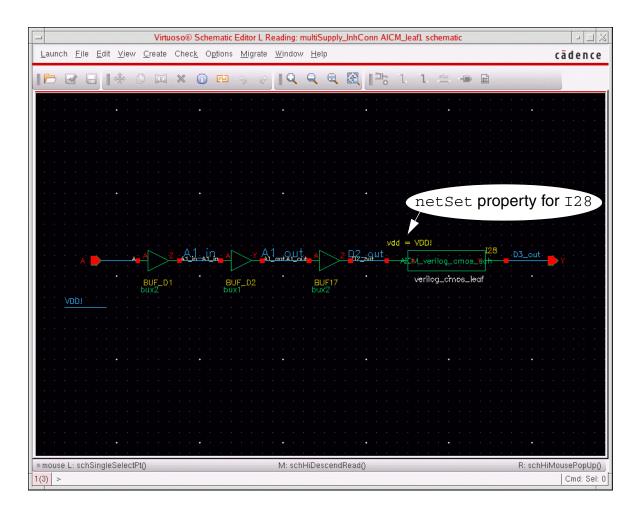

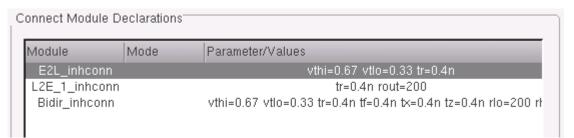

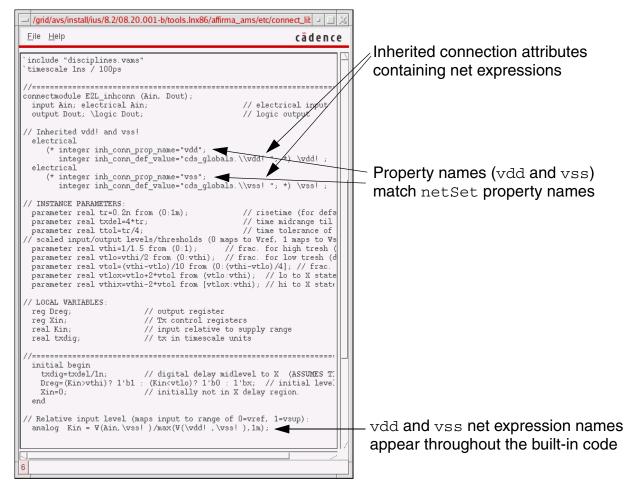

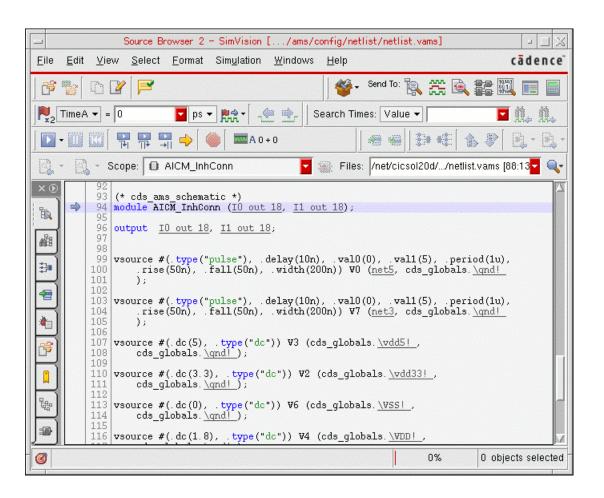

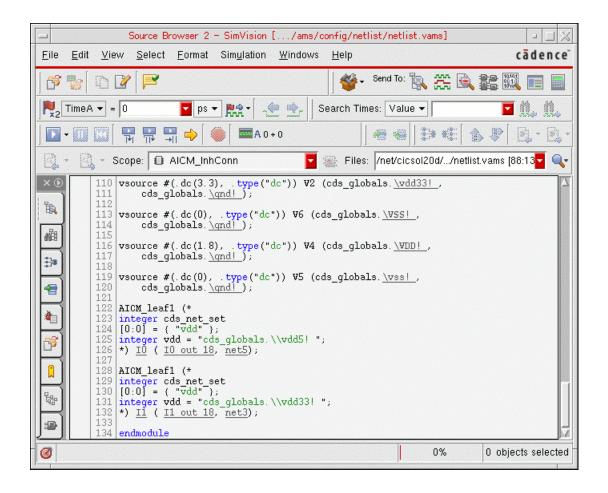

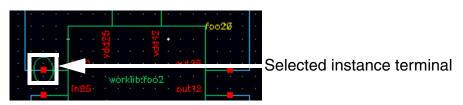

**12.** On the Rename Connect Rules form, edit the name of the rule to be My\_ConnRules\_25V\_full\_fast.