Product Version 6.1.6 August 2014 © 2006–2014 Cadence Design Systems, Inc. All rights reserved.

Portions © Regents of the University of California, Sun Microsystems, Inc., Scriptics Corporation. Used by permission.

Printed in the United States of America.

Cadence Design Systems, Inc. (Cadence), 2655 Seely Ave., San Jose, CA 95134, USA.

Product AMS contains technology licensed from, and copyrighted by: Regents of the University of California, Sun Microsystems, Inc., Scriptics Corporation, and other parties and is © 1989-1994 Regents of the University of California, 1984, the Australian National University, 1990-1999 Scriptics Corporation, and other parties. All rights reserved.

Open SystemC, Open SystemC Initiative, OSCI, SystemC, and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission.

**Trademarks**: Trademarks and service marks of Cadence Design Systems, Inc. contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 800.862.4522. All other trademarks are the property of their respective holders.

**Restricted Permission:** This publication is protected by copyright law and international treaties and contains trade secrets and proprietary information owned by Cadence. Unauthorized reproduction or distribution of this publication, or any portion of it, may result in civil and criminal penalties. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. Unless otherwise agreed to by Cadence in writing, this statement grants Cadence customers permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used only in accordance with a written agreement between Cadence and its customer.

- 2. The publication may not be modified in any way.

- 3. Any authorized copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement.

- 4. The information contained in this document cannot be used in the development of like products or software, whether for internal or external use, and shall not be used for the benefit of any other party, whether or not for consideration.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor

# Contents

| Preface                                            | 21 |

|----------------------------------------------------|----|

| Scope of this Guide                                | 22 |

| _icensing for the AMS Designer Environment         | 22 |

| Related Documents for the AMS Designer Environment | 22 |

| Third-Party Software for Viewing Video Clips       | 23 |

| Typographic and Syntax Conventions                 | 23 |

| Data Type Prefixes for SKILL Arguments             | 26 |

| Additional Learning Resources                      | 27 |

# 1

| Getting Started with AMS Designer 29                          |

|---------------------------------------------------------------|

| Setting Up the Tutorial                                       |

| Running the Tutorial in the AMS Designer Environment          |

| Opening the Schematic and Design Configuration                |

| Initializing AMS                                              |

| Using the Quick Setup Form                                    |

| Using the Netlist and Run Form                                |

| Running the Simulation                                        |

| Using the SimVision Source Browser 60                         |

| Using the SimVision Waveform Window                           |

| Running the Tutorial Using the UltraSim Analog Solver         |

| Switch to Using the UltraSim Solver                           |

| Specify Incremental Netlisting, Compilation, and Elaboration  |

| Change the Simulation Snapshot Name                           |

| Run the Simulation Using the UltraSim Solver and View Results |

| Running the Tutorial from the Command Line                    |

## <u>2</u>

| Setting Up the AMS          | Designer Environment | 69 |

|-----------------------------|----------------------|----|

| Understanding TMP Libraries |                      | 71 |

| Understanding Explicit TMP Libraries                 |

|------------------------------------------------------|

| Understanding Implicit TMP Libraries                 |

| Specifying Preferences for Netlisting and Compiling  |

| Importing Customized Built-In Connect Rules from ADE |

| Opening a config View in the Hierarchy Editor        |

| Adding AMS to the Menu Bar in the Hierarchy Editor   |

| Initializing the AMS Designer Environment            |

| Specifying an Existing Run Directory                 |

| Specifying a New Run Directory                       |

| Using Quick Setup                                    |

# <u>3</u>

| Using the Netlist and Run Form 88                                  | 5 |

|--------------------------------------------------------------------|---|

| Specifying the Netlister and the Run Mode                          | 8 |

| Specifying Run Options                                             | 9 |

| Specifying the Transient Stop Time 89                              | 9 |

| Specifying Model Libraries for Simulation                          | 0 |

| Specifying Simulation Options                                      | 0 |

| Specifying Outputs to Save and to Plot                             | 0 |

| Specifying the Simulation Mode                                     | 1 |

| Specifying Connect Rules                                           |   |

| Adding or Changing a Single Connect Rule                           | 2 |

| Specifying More than One Set of Connect Rules or Customizing Rules | 3 |

| Specifying the Global Design Data Module                           | 4 |

| Specifying the Simulation Snapshot Name and Location               | 4 |

| Specifying Local, Remote, or Distributed Simulation                | 5 |

| Specifying Local Simulation                                        | 5 |

| Specifying Remote Simulation                                       | 5 |

| Specifying Distributed Simulation                                  | 6 |

| Important Information about Remote and Distributed Simulations     | 6 |

| Using the Buttons at the Bottom of the Form                        | 7 |

# <u>4</u>

| Using the Detailed Setup Menu.               |  |

|----------------------------------------------|--|

| Specifying Analog Solver and Waveform Viewer |  |

| Specifying an Analysis                          |

|-------------------------------------------------|

| Specifying a Transient Analysis 103             |

| Specifying a DC Analysis                        |

| Specifying an AC Analysis (Spectre Solver Only) |

| Specifying an Envelope Analysis                 |

| Specifying Model Libraries                      |

| Specifying Design Variables 113                 |

| Specifying Connect Rules                        |

| Specifying Outputs to Save and to Plot 114      |

| Specifying Spectre Options                      |

| Specifying UltraSim Options                     |

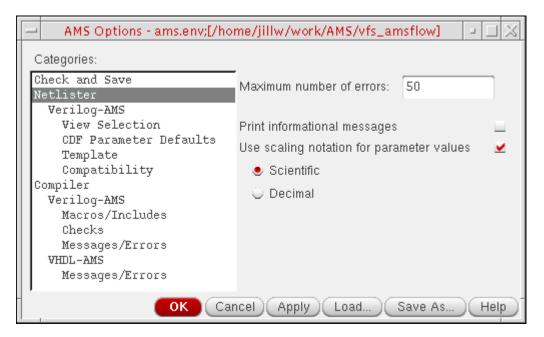

| Specifying AMS Options                          |

| Specifying Environment Options                  |

| Specifying Data Save Options                    |

| Saving Data for Nets and Ports                  |

| Saving Current Data                             |

| Saving Other Design Information                 |

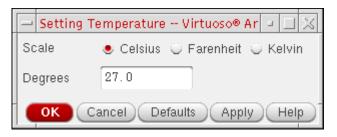

| Specifying Simulation Temperature 122           |

| Specifying Simulation Files                     |

| Specifying Global Signals                       |

| Specifying Nodesets                             |

| Specifying Initial Conditions                   |

|                                                 |

# <u>5</u>

| Using the AMS Options Form 12                             | 25 |

|-----------------------------------------------------------|----|

| Opening the AMS Options Form                              | 27 |

| Specifying a Tcl Input Script 13                          | 30 |

| Specifying Library Files and Directories for the Compiler | 32 |

| Specifying an hdl.var File                                | 34 |

| Specifying a Verilog-AMS Macro to Use during Compilation  | 35 |

| Specifying an Include Path 13                             | 36 |

| Specifying Default Timescale Options 13                   | 39 |

| Specifying Discipline Options 14                          | 11 |

| Specifying Additional Arguments for the Elaborator        | 13 |

| Specifying Additional Arguments for the Simulator         | 14 |

| Controlling Messages for the Compiler, Elaborator, and Simulator |

|------------------------------------------------------------------|

| Specifying VPI and PLI Options                                   |

| Disabling Constraint Checking in VHDL Design Access Functions    |

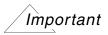

| Specifying SDF Annotation Options for the Elaborator             |

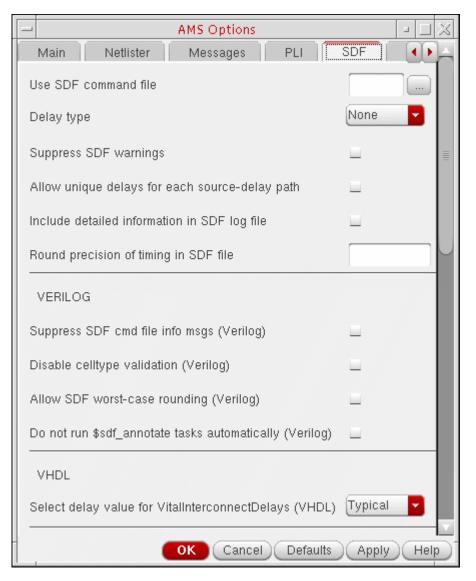

| Specifying Timing Check Options 156                              |

| Specifying Verilog Timing Options 157                            |

| Specifying VHDL Timing Options 162                               |

| Specifying Access Options                                        |

| Specifying Profiler Options                                      |

| Specifying Linter Checking Options                               |

| Specifying Other Options                                         |

|                                                                  |

## <u>6</u>

# Performing Miscellaneous Tasks in the AMS DesignerEnvironment169Displaying the Netlist170Loading State Files170Saving State Files170Generating the AMS Netlist for a Cell171Viewing the AMS Netlist for a Cell171Compiling the AMS Netlist for a Cell171

## <u>7</u>

| Using Design Configurations                            | 173 |

|--------------------------------------------------------|-----|

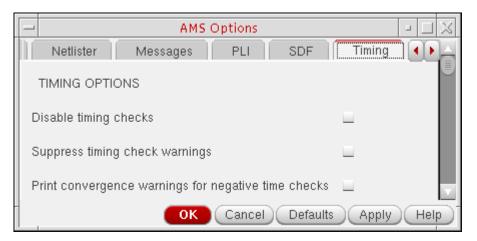

| Understanding Configurations                           | 174 |

| Creating a Config Cellview                             | 175 |

| Using VHDL Design Units in a Configuration             | 176 |

| Netlisting to Make HDL Design Unit Information Current | 176 |

| Using a Configuration                                  | 177 |

### <u>8</u>

| Netlisting                         | 179 |

|------------------------------------|-----|

| Using the OSS Netlister            | 179 |

| Using the Cellview-Based Netlister | 180 |

| Automatic Netlisting                                                   |

|------------------------------------------------------------------------|

| Netlisting the Entire Design                                           |

| Netlisting Incrementally                                               |

| Library Netlisting from the CIW                                        |

| Netlisting Cells in Response to Changes in CDF                         |

| Netlisting from the UNIX Command Line 189                              |

| Specifying AMS Netlister Options                                       |

| Maximum Number of Errors 193                                           |

| Print Informational Messages 194                                       |

| Include Files                                                          |

| Header Text                                                            |

| Default Global Signal Declarations 198                                 |

| <u>Global Signals</u>                                                  |

| <u>Global Design Data Module (cds_globals)</u> 200                     |

| Specifying Netlist Format for Component Instances for AMS Simulation   |

| Excluding Parameters from Netlisting 203                               |

| Excluding Parameters from Netlisting for an Entire Library             |

| Excluding Parameters from Netlisting for a Cell                        |

| Viewing the AMS Netlister Log File                                     |

| Understanding How the Cellview-Based Netlister Operates                |

| Passing Information to the Elaborator 209                              |

| Netlisting Inherited Connections                                       |

| Netlisting Inherited Terminal Connections 211                          |

| Netlisting netSet Properties                                           |

| Netlisting Aliased Signals                                             |

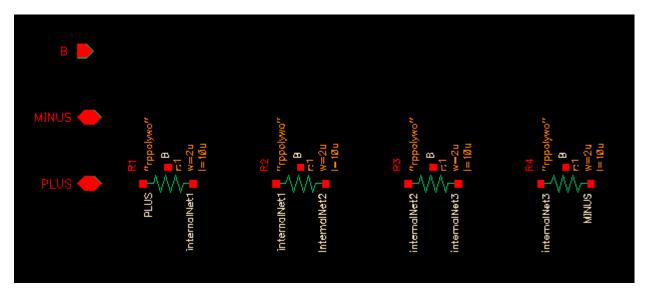

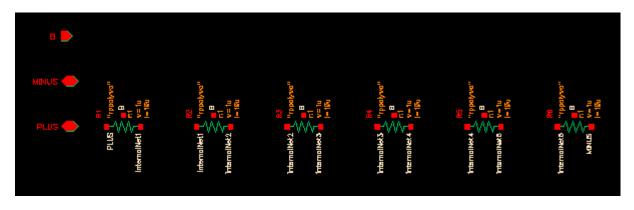

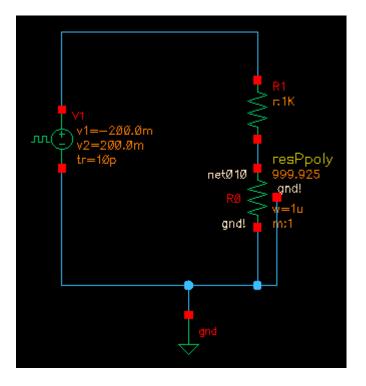

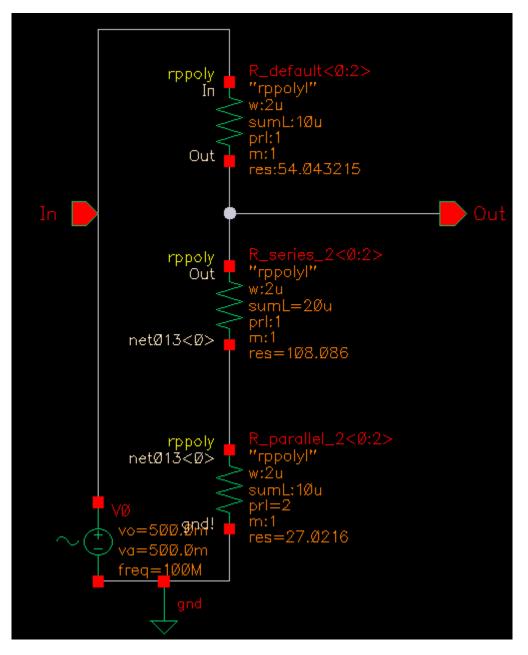

| Netlisting Multiplicity Factors                                        |

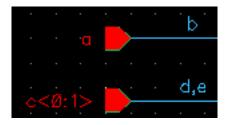

| Netlisting Iterated Instances                                          |

| Netlisting Model Names from Parameter Values                           |

| Netlisting componentName Parameters 218                                |

| Forcing Schematic Parameter Values to Netlist as Floating Point Values |

# <u>9</u>

| Working with Schematic Designs                       | 223 |

|------------------------------------------------------|-----|

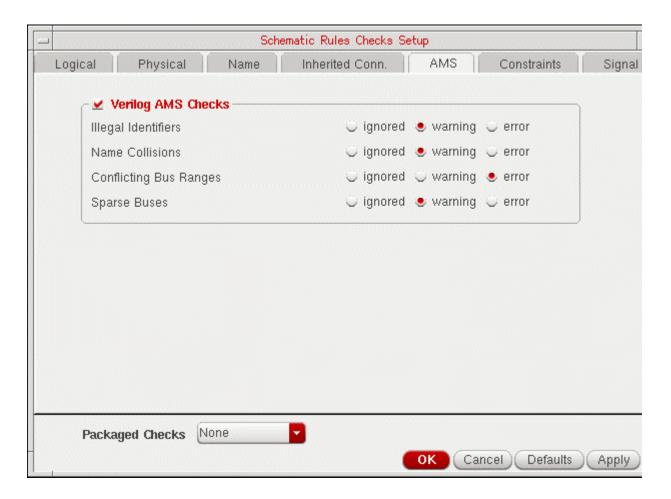

| Specifying Schematic Rules Checking for AMS Designer | 224 |

| Language Noncompliance                               | 227 |

| System-Generated Names                                           |

|------------------------------------------------------------------|

| Bus Range Conflicts                                              |

| <u>Sparse Buses</u>                                              |

| Creating Cellviews Using the AMS Designer Environment            |

| Creating a New Library                                           |

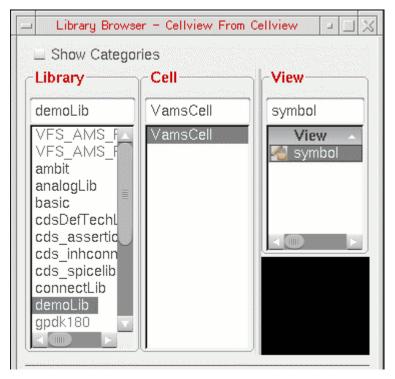

| Creating a Schematic Symbol View for a Verilog-AMS Module        |

| Creating a Block to Represent a Verilog-AMS Module               |

| Creating a Verilog-AMS Cellview from an Existing Symbol or Block |

| Creating a VHDL-AMS Cellview from an Existing Symbol or Block    |

| Creating HDL Source Files Outside the AMS Designer Environment   |

| Creating a New Verilog-AMS Module Cellview                       |

| Creating a New VHDL-AMS Module Cellview                          |

| Creating a Symbol Cellview from a Verilog-AMS Cellview           |

| Viewing Source Code for an HDL Cellview                          |

| Using Net and Pin Properties 248                                 |

| groundSensitivity and supplySensitivity Properties               |

| Making Connect Modules Sensitive to Ground and Supply            |

|                                                                  |

# <u>10</u>

| Using External Text Designs                                 | 257 |

|-------------------------------------------------------------|-----|

| Specifying the Working Library                              | 258 |

| Compiling a Module into a Library                           | 259 |

| Compiling into Temporary Libraries                          | 261 |

| Binding to a New Cellview in a Temporary Library            | 261 |

| Creating a Configuration with a View List for AMS           | 263 |

| Opening the New Configuration Form from the CIW             | 264 |

| Opening the New Configuration Form from the Library Manager | 264 |

| Creating a cds globals Module for External Text Designs     | 265 |

## <u>11</u>

| Using Existing Analog Design Units                    | 267 |

|-------------------------------------------------------|-----|

| Preparing to Use SPICE and Spectre Design Units       | 268 |

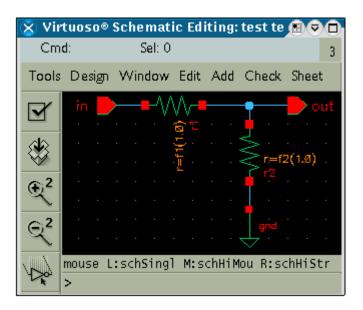

| Placing SPICE and Spectre Design Units on a Schematic | 269 |

| Editing AMS Simulation Information                    | 269 |

# <u>12</u>

| Creating and Using a Test Fixture Module                                          | 271 |

|-----------------------------------------------------------------------------------|-----|

| Creating a Verilog-AMS Test Fixture in the AMS Designer Environment               | 273 |

| Creating a Verilog-AMS Test Fixture Outside the AMS Designer Environment          | 274 |

| Creating and Testing a Verilog-AMS Switch Module Using a Verilog-AMS Test Fixture | 274 |

# <u>13</u>

| Specifying Compiler Options                        | 277 |

|----------------------------------------------------|-----|

| Specifying Libraries to Exclude during Compilation | 278 |

| Compiling Digital Verilog without the -ams Option  | 280 |

| Turning On Line Debug for SimVision                | 282 |

| Specifying Additional Verilog Compiler Arguments   | 283 |

| Specifying Additional VHDL Compiler Arguments      | 284 |

# <u>14</u>

| Viewing Simulation Output       | 5  |

|---------------------------------|----|

| Listing Compiled Modules        | 6  |

| Plotting Results                | 57 |

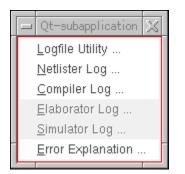

| Using the Log File Utility      | 9  |

| Viewing the Netlister Log File  | 9  |

| Viewing the Compiler Log File   | 9  |

| Viewing the Elaborator Log File | 9  |

| Viewing the Simulator Log File  | 0  |

| Viewing Error Explanations      | 0  |

# <u>15</u>

| Using the amsdesigner Command                  |  |

|------------------------------------------------|--|

| Using Existing or Creating New Run Directories |  |

| Examples                                       |  |

#### 16 Identifying the Sections of a Netlist Using Netlisting Procedures to Customize Netlists Writing and Loading Netlisting Procedures Choosing the Best Customization Approach Addressing Problems using Customized Netlists Using CDF Instance Parameters to Define Inherited Connections Formatter Object Parameter Object Instance Object Port Object IO Object Alias Object

# <u>A</u>

| Variables for ams.env Files 35             |

|--------------------------------------------|

| List of ams.env Variables                  |

| Detailed Descriptions of ams.env Variables |

| aliasInstFormat                            |

| <u>allowDeviantBuses</u>                   |

| <u>allowIllegalIdentifiers</u>             |

| allowNameCollisions                        |

| <u>allowSparseBuses</u>                    |

| allowUndefParams                           |

| amsCompMode               |

|---------------------------|

| amsDefinitionViews        |

| amsEligibleViewTypes      |

| amsExcludeParams          |

| amsExpScalingFactor       |

| <u>amsLSB_MSB</u>         |

| amsMaxErrors              |

| amsScalarInstances        |

| <u>amsVerbose</u>         |

| analogControlFile         |

| artistStateDirectory      |

| bindCdsAliasLib           |

| bindCdsAliasView          |

| <u>cdsGlobalsLib</u>      |

| cdsGlobalsView            |

| checkAndNetlist           |

| <u>checkOnly</u>          |

| <u>checktasks</u>         |

| <u>compileAsAMS</u>       |

| compileExcludeLibs        |

| <u>compileMode</u>        |

| confirmADEStateImport     |

| connectRulesCell          |

| connectRulesCell2         |

| connectRulesLib           |

| connectRulesView          |

| defaultRunDir             |

| detailedDisciplineRes     |

| <u>discipline</u>         |

| errOutInconsistentMasters |

| excludeViewNames          |

| hdlVarFile                |

| <u>headerText</u>         |

| <u>ieee1364</u>           |

| ifdefLanguageExtensions   |

| ignoreIllegalCDFParams    |

| implicitTmpDir                              |

|---------------------------------------------|

| incdir                                      |

| includeFiles                                |

| includeInstCdfParams                        |

| <u>initFile</u>                             |

| instClashFormat                             |

| iterInstExpFormat                           |

| language                                    |

| lexpragma                                   |

| logFileAction                               |

| logFileName                                 |

| <u>macro</u>                                |

| markcelldefines                             |

| <u>maxErrors</u>                            |

| <u>messages</u>                             |

| modifyParamScope                            |

| <u>ncelabAccess</u>                         |

| <u>ncelabAfile</u>                          |

| ncelabAnnoSimtime                           |

| ncelabArguments                             |

| <u>ncelabCoverage</u>                       |

| ncelabDelayMode                             |

| ncelabDelayType through ncelabMessages 440  |

| <u>ncelabMixEsc</u>                         |

| ncelabModelFilePaths                        |

| ncelabNeverwarn through ncelabVipdelay 443  |

| ncsimArguments                              |

| ncsimEpulseNoMsg through ncsimExtassertmsg  |

| <u>ncsimGUI</u>                             |

| ncsimLoadvpi through ncsimStatus 449        |

| <u>ncsimTcl</u>                             |

| ncsimUnbuffered through ncsimUseAddArgs 451 |

| ncvhdlArguments                             |

| <u>ncvlogArguments</u>                      |

| ncvlogUseAddArgs                            |

| netClashFormat                              |

| netlistAfterCdfChange |

|-----------------------|

| netlistMode           |

| netlistToRunDir       |

| netlistUDFAsMacro     |

| <u>neverwarn</u>      |

| noline                |

| nomempack             |

| nopragmawarn          |

| nostdout              |

| nowarn                |

|                       |

| paramDefVals          |

| paramGlobalDefVal     |

| <u>pragma</u>         |

| useRunDirNetlistsOnly |

| processViewNames      |

| prohibitCompile       |

| <u>runNcelab</u>      |

| <u>runNcsim</u>       |

| scaddlglblopts        |

| scaddltranopts        |

| <u>scale</u>          |

| <u>scalem</u>         |

| scannotate            |

| <u>scapprox</u>       |

| <u>scaudit</u>        |

| <u>sccheckstmt</u>    |

| sccmin                |

| sccompatible 487      |

| <u>scdebuq</u>        |

| scdiagnose            |

| <u>scdigits</u>       |

| <u>scerror</u>        |

| scerrpreset           |

| scfastbreak           |

| scqlobalminr          |

| <u>scgnin</u>         |

| <u></u>               |

| scgmincheck         |

|---------------------|

| <u>schomotopy</u>   |

| <u>sciabstol</u>    |

| <u>scic</u>         |

| <u>scicstmt</u>     |

| scignshorts         |

| <u>scinfo</u>       |

| <u>scinventory</u>  |

| <u>sclimit</u>      |

| sciteratio          |

| scmacromod          |

| scmaxiters          |

| scmaxnotes          |

| scmaxnotestologfile |

| <u>scmaxrsd</u>     |

| <u>scmaxstep</u>    |

| <u>scmaxwarn</u>    |

| scmaxwarntologfile  |

| <u>scmethod</u>     |

| scmodelevaltype     |

| <u>scmosvres</u>    |

| <u>scnarrate</u>    |

| scnotation          |

| <u>scnote</u>       |

| scopptcheck         |

| <u>scpivabs</u>     |

| <u>scpivotdc</u>    |

| <u>scpivrel</u>     |

| scquantities        |

| <u>screadic</u>     |

| <u>screadns</u>     |

| <u>screlref</u>     |

| <u>screltol</u>     |

| <u>scrforce</u>     |

| <u>scscale</u>      |

| scscalem            |

| scscfincfile        |

|---------------------|

| scscftimestamp      |

| scscfusefileflag    |

| scskipcount         |

| scskipdc            |

| <u>scskipstart</u>  |

| <u>scskipstop</u>   |

| <u>scspeed</u>      |

| scspscflag          |

| <u>scstats</u>      |

| <u>scstep</u>       |

| <u>scstop</u>       |

| scstrobedelay       |

| scstrobeperiod      |

| <u>sctemp</u>       |

| sctempeffects       |

| <u>sctitle</u>      |

| <u>sctnom</u>       |

| <u>sctopcheck</u>   |

| scusemodeleval      |

| scvabstol           |

| scwarn              |

| scwrite             |

| scwritefinal        |

| simcompat           |

| <u>simRunDirLoc</u> |

| simVisScriptFile    |

| <u>status</u>       |

| templateFile        |

| templateScript      |

| timescale           |

| <u>update</u>       |

| <u>use5xForVHDL</u> |

| <u>useDefparam</u>  |

| useEffectiveCDF     |

| useNcelabNowarn     |

| useNcelabSdfCmdFile            |

|--------------------------------|

| useNcsimNowarn                 |

| <u>useNowarn</u>               |

| useProcessViewNamesOnly        |

| useScaddlglblopts              |

| useScaddltranopts              |

| <u>useScic</u>                 |

| <u>useScreadic</u>             |

| <u>useScreadns</u>             |

| useScscfincfile                |

| <u>useScwrite</u>              |

| useScwritefinal                |

| useSimVisScriptFile            |

| usimAbstoli through usimWFTres |

| verboseUpdate                  |

| vlogGroundSigs                 |

| <u>vloglinedebug</u>           |

| <u>vlogSupply0Sigs</u>         |

| vlogSupply1Sigs                |

| wfDefaultDatabase              |

| wfDefInstCSaveAll              |

| wfDefInstCSaveLvl              |

| wfDefInstSaveCurrents          |

| wfDefInstSaveVoltages          |

| wfDefInstVSaveAll              |

| wfDefInstVSaveLvI              |

| wfDefInstVSaveObjects          |

| <u>wfFilter</u>                |

| wfFilterSpec                   |

# <u>B</u>

| CIW Interface for AMS Designer                | 601 |

|-----------------------------------------------|-----|

| Specifying Automatic Netlisting from the CIW  | 602 |

| Library Netlisting from the CIW               | 603 |

| Specifying AMS Netlister Options from the CIW | 607 |

|    | Maximum Number of Errors                              | 608 |

|----|-------------------------------------------------------|-----|

|    | Print Informational Messages                          | 609 |

|    | Use Scaling Notation for Parameter Values             | 610 |

|    | Include Files                                         | 611 |

|    | Header Text                                           | 613 |

|    | Conditionally Include Verilog-AMS Language Extentions | 617 |

|    | Eligible View Types and View Names to Exclude         | 619 |

|    | View Names to Process                                 | 621 |

|    | CDF Parameter Defaults                                | 623 |

|    | Verilog-AMS Compatibility Exceptions                  | 625 |

|    | Netlisting User-Defined Functions                     | 626 |

| Sp | pecifying Compiler Options from the CIW               | 628 |

|    | hdl.var File                                          | 629 |

|    | Verilog-AMS Compiler Options                          | 631 |

|    | Verilog-AMS Macros to Use during Compilation          | 634 |

|    | Directories to Search for Verilog-AMS Include Files   | 636 |

|    | Checks for Verilog-AMS Modules                        | 638 |

|    | Verilog-AMS Compiler Message Options                  | 640 |

|    | VHDL-AMS Compiler Options                             | 642 |

|    | VHDL-AMS Compiler Message Options                     | 645 |

# <u>C</u>

| Updating Legacy SimInfo for Analog Primitives 647 |

|---------------------------------------------------|

| The ams Fields                                    |

| otherParameters                                   |

| instParameters                                    |

| enumParameters                                    |

| referenceParameters                               |

| stringParameters                                  |

| arrayParameters                                   |

| excludeParameters                                 |

| <u>componentName</u>                              |

| <u>termOrder</u>                                  |

| termMapping                                       |

| propMapping                                       |

| extraTerminals                                                     | 657 |

|--------------------------------------------------------------------|-----|

| isPrimitive                                                        | 658 |

| Special Handling of model, modelName, modelname, and componentName | 660 |

| Converting an Existing Analog Primitive Library                    | 660 |

# <u>D</u>

| Designing for Virtuoso AMS Compliance                                       |  |

|-----------------------------------------------------------------------------|--|

| Identifiers                                                                 |  |

| Follow the Recommended Syntax for Identifiers                               |  |

| Ensure that Identifiers Map Cleanly to Netlist Languages                    |  |

| Ensure That Identifiers Are Unique within Your Design                       |  |

| <u>Terminals</u>                                                            |  |

| <u>Buses</u>                                                                |  |

| Component Description Format                                                |  |

| <u>Parameters</u>                                                           |  |

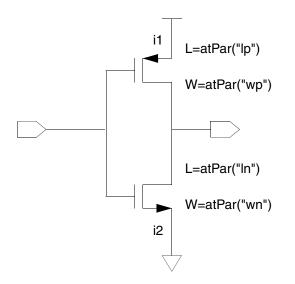

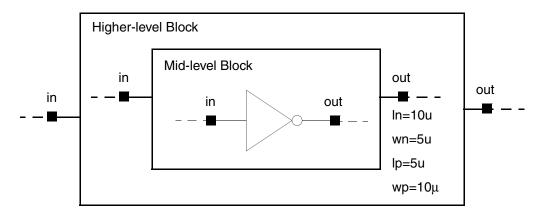

| Using Inherited Parameters                                                  |  |

| Using Cell Parameters                                                       |  |

| Using Efficient Formats for Parameter Values                                |  |

| Parameterized Cells                                                         |  |

| VHDL-AMS Component Declarations                                             |  |

| <u>Properties</u>                                                           |  |

| Properties to Avoid Completely                                              |  |

| Avoid the portOrder Property Unless Required by Special Circumstances       |  |

| Properties to Use Only in AMS Compatibility Mode                            |  |

| Properties That Have No Special Meaning in the AMS Designer Environment 676 |  |

| Properties Fully Supported by the AMS Designer Environment                  |  |

# <u>E</u>

| Customization Variables        | 679 |

|--------------------------------|-----|

| Customization Variables        | 679 |

| schHdlNotCreateDB              | 681 |

| <u>schHdlUseVamsForVerilog</u> | 682 |

| <u>vhdlCrossViewCheck</u>      | 682 |

| vhdlKeepCaseAsNC               | 683 |

| vhdlUpdateSymbol               | 684 |

| <u>vmsAnalysisType</u>          | 685 |

|---------------------------------|-----|

| vmsCreateMissingMasters         | 686 |

| <u>vmsCrossViewCheck</u>        | 686 |

| vmsDoNotCheckMasterFileWritable | 687 |

| vmsNcvlogExecutable             | 688 |

| vmsPortProcessing               | 689 |

| vmsRunningInUI                  | 690 |

| vmsTemplateScript               | 691 |

| vmsUpdateSymbolAfterEdit        | 692 |

| <u>vmsVerboseMsgLevel</u>       | 693 |

| <u>E</u>                             |     |

|--------------------------------------|-----|

| Compiling Cadence-Provided Libraries | 695 |

## <u>G</u>

| <u>V</u>                                             |            |

|------------------------------------------------------|------------|

| Migrating from Previous Versions of the AMS Designer |            |

| Environment 69                                       | <b>)</b> 7 |

| The ams.env File                                     | <b>)</b> 7 |

| AMS Design Prep Form                                 | <b>)</b> 7 |

| AMS Options for Global Design Data 69                | 98         |

| AMS Direct Plot Form                                 | 98         |

| AMS Designer Simulations                             | 98         |

|                                                      |            |

| Index                                                | 99         |

The Virtuoso<sup>®</sup> AMS Designer environment provides a framework for developing, simulating, and debugging mixed-signal design blocks. Using the AMS Designer environment, you can

- Design mixed-signal, mixed-language blocks in an environment that supports both schematic and text data entry

- Access AMS forms and features from the <u>Cadence Hierarchy Editor</u>, the <u>schematic</u> <u>editor</u>, or the <u>command interpreter window</u>

- Set up, netlist, and run your AMS simulation automatically from the schematic environment or completely standalone from the command line

- Create netlists:

- a (full or incremental) netlist for an entire design

- □ a netlist for an entire library

- Simulate using the Spectre, UltraSim or APS solver of the AMS Designer simulator

- Import and use Tcl command and analog simulation control files

- Interactively debug your design and investigate the results

- Display analog, digital, and mixed-signal waveforms in one enviroment

**Note:** Cadence offers the Virtuoso Analog Design Environment (<u>ADE</u>) for analog-oriented designs. ADE shares many of the same forms, functionality, state files, and default mechanisms with the AMS Designer environment but caters to analog designs.

To get started, see Chapter 1, "Getting Started with AMS Designer."

See the following topics for additional information in this preface:

- <u>Scope of this Guide</u> on page 22

- Licensing for the AMS Designer Environment on page 22

- Related Documents for the AMS Designer Environment on page 22

- <u>Third-Party Software for Viewing Video Clips</u> on page 23

- <u>Typographic and Syntax Conventions</u> on page 23

- Data Type Prefixes for SKILL Arguments on page 26

- Additional Learning Resources on page 27

# Scope of this Guide

All the functionality described in this guide is available in IC6.1.6 and ICADV12.1 onward unless otherwise noted. Features that are supported only in a particular release are identified using (ICADV12.1 only) and (IC6.1.6 only) labels.

# Licensing for the AMS Designer Environment

There is no licensing information specific to the Virtuoso<sup>®</sup> AMS Designer environment. General licensing information for the Virtuoso design environment is available in the <u>Virtuoso</u> <u>Software Licensing and Configuration User Guide</u>.

# **Related Documents for the AMS Designer Environment**

For more information about the AMS simulator and related products, consult the sources listed below.

- <u>Cadence Application Infrastructure User Guide</u>

- <u>Cadence Hierarchy Editor User Guide</u>

- <u>Virtuoso AMS Designer Environment SKILL Reference</u>

- <u>Cadence Library Manager User Guide</u>

- <u>Cadence Verilog-AMS Language Reference</u>

- Cadence VHDL-AMS Overview

- Component Description Format User Guide

- IEEE Std 1076.1. Available from IEEE.

- Instance-Based View Switching Application Note

- Virtuoso NC Verilog Environment User Guide

- *Verilog-AMS Language Reference Manual*. Available from Open Verilog International.

- <u>Virtuoso AMS Designer Simulator User Guide</u>

- Virtuoso Analog Design Environment User Guide

- Virtuoso Mixed-Signal Circuit Design Environment User Guide

- Virtuoso Schematic Editor User Guide

- Virtuoso Spectre Circuit Simulator Reference

- Virtuoso Spectre Circuit Simulator and Accelerated Parallel Simulator User Guide

- Virtuoso UltraSim Simulator User Guide

- Virtuoso Parasitic Simulation User Guide

For information about problems, see the *Virtuoso AMS Designer Environment Known Problems and Solutions*.

# **Third-Party Software for Viewing Video Clips**

To view any .swf multimedia files (which appear as <u>Show Me</u> hot links), you need:

Access to the <u>Cadence Online Support</u> website.

Contact your CAD department or your local Cadence representative for information about obtaining access to the <u>Cadence Online Support</u> website.

Note: For access to the entire CIC Video Library, click here.

- Flash-enabled web browser such as Internet Explorer 5.0 or later, Netscape 6.0 or later, or Mozilla Firefox 1.6 or later. Alternatively, you can download Flash Player (version 6.0 or later) directly from the <u>Adobe</u> website.

- Speakers and a sound card for videos that have audio narration.

# **Typographic and Syntax Conventions**

In general, the text in this book follow these typographic and syntax conventions:

| text       | Indicates text you must type exactly as it is presented.                                                                       |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| z_argument | Indicates text that you must replace with an appropriate argument. The prefix (in this case, $z_{-}$ ) indicates the data type |  |  |

the argument can accept. Do not type the data type or underscore.

- [ ] Denotes an optional argument. When used with vertical bars, they enclose a list of choices from which you can choose one.

- { } Used with vertical bars, they denote a list of choices from which you must choose one.

- Separates a choice of options.

- ... Indicates that you can repeat the previous argument.

- => Precedes the values returned by a Cadence<sup>®</sup> SKILL language function.

- / Separates the possible values that can be returned by a Cadence SKILL language function.

- *text* Indicates names of manuals, menu commands, form buttons, and form fields.

For other more specialized text, the following typographical conventions apply:

- The definition operator, ::=, defines more complex elements of the Verilog-AMS language in terms of less complex elements.

- Lowercase words represent syntactic categories. For example,

module\_declaration

Some names begin with a part that indicates how the name is used. For example,

node\_identifier

represents an identifier that is used to declare or reference a node.

Boldface words represent elements of the syntax that must be used exactly as presented (except as noted below). Such items include keywords, operators, and punctuation marks. For example,

#### endmodule

Sometimes options can be abbreviated. The shortest permitted abbreviation is shown by capital letters but you can use either upper or lower-case letters in your code. For example, the syntax

#### -CHecktasks

means that you can type the option as -checktasks, -CHECKTASKS, -ch, -cH, -cH, and so on.

Vertical bars indicate alternatives. You can choose to use any one of the items separated by the bars. For example,

```

attribute ::=

abstol

laccess

lddt_nature

lidt_nature

lunits

lhuge

lblowup

lidentifier

```

■ Square brackets enclose optional items. For example,

```

input declaration ::=

input [ range ] list of port identifiers ;

```

■ Braces enclose an item that you can specify zero or more times. For example,

```

list_of_ports ::=

( port { , port } )

```

■ Code examples appear in constant-width font.

```

/* This is an example of the font used for code.*/

```

- Within the text, variables are in italic font, like this: *allowed\_errors*.

- Keywords, filenames, names of natures, and names of disciplines appear in constantwidth font, like this:

```

keyword

file_name

name_of_nature

name_of_discipline

```

If a statement is too long to fit on one line, the remainder of the statement appears indented on the next line, like this:

## **Data Type Prefixes for SKILL Arguments**

The Cadence SKILL language supports several data types to identify the type of value you can assign to an argument. You can determine the data type by the single letter (followed by an underscore) that appears as a prefix on an argument name as follows:

| Prefix | Internal Name         | Data Type                                  |

|--------|-----------------------|--------------------------------------------|

| a      | array                 | array                                      |

| b      | ddUserType            | DDPI Object                                |

| С      | opfcontext            | OPF context                                |

| d      | dbobject              | Open Access database (OA)                  |

| е      | envobj                | environment                                |

| f      | flonum                | floating-point number                      |

| F      | opffile               | OPF file ID                                |

| g      | general               | any data type                              |

| G      | gdmSpecIIUserType     | gdm spec                                   |

| h      | hdbobject             | hierarchical database configuration object |

| 1      | list                  | linked list                                |

| т      | nmpIIUserType         | nmpll user type                            |

| М      | cdsEvalObject         | —                                          |

| п      | number                | integer or floating-point number           |

| 0      | userType              | user-defined type (other)                  |

| р      | port                  | I/O port                                   |

| q      | gdmspecListIIUserType | gdm spec list                              |

| r      | defstruct             | defstruct                                  |

| R      | rodObj                | relative object design (ROD) object        |

| S      | symbol                | symbol                                     |

| S      | stringSymbol          | symbol or character string                 |

| t      | string                | character string (text)                    |

Preface

| Prefix | Internal Name | Data Type                                                                                |  |  |  |  |

|--------|---------------|------------------------------------------------------------------------------------------|--|--|--|--|

| и      | function      | function object, either the name of a function (symbol) or a lambda function body (list) |  |  |  |  |

| U      | funobj        | function object                                                                          |  |  |  |  |

| V      | hdbpath       | —                                                                                        |  |  |  |  |

| W      | wtype         | window type                                                                              |  |  |  |  |

| X      | integer       | integer number                                                                           |  |  |  |  |

| У      | binary        | binary function                                                                          |  |  |  |  |

| &      | pointer       | pointer type                                                                             |  |  |  |  |

For example, *t* is the data type in *t\_viewNames*.

For example, *t* is the data type in *t\_viewNames*.

For information on the SKILL language, see the *Cadence SKILL Language User Guide*.

## **Additional Learning Resources**

Cadence provides various <u>Rapid Adoption Kits</u> that you can use to learn how to employ Virtuoso applications in your design flows. These kits contain workshop databases, designs, and instructions to run the design flow.

Cadence offers the following training courses on Virtuoso AMS Designer Environment:

- Virtuoso Schematic Editor

- Virtuoso Analog Design Environment

- Analog Modeling with Verilog-A

- Behavioral Modeling with Verilog-AMS

- Real Modeling with Verilog-AMS

For further information on the training courses available in your region, visit the <u>Cadence</u> <u>Training</u> portal. You can also write to training\_enroll@cadence.com.

**Note:** The links in this section open in a new browser. They initially display the requested training information for North America, but if required, you can navigate to the courses available in other regions.

# Getting Started with AMS Designer

The Virtuoso<sup>®</sup> AMS Designer environment and simulator work together so that you can set up your simulation, netlist, compile, elaborate, and simulate designs that contain analog, digital, and mixed-signal components. You can run simulations in batch mode or interactively using the SimVision debugger. When the simulation is complete, you can view waveforms using SimVision or the <u>Virtuoso Visualization and Analysis</u> program. The AMS Designer simulator lets you switch between using the Spectre, UltraSim and the APS solvers. See also <u>Chapter 8, "Netlisting"</u> for information about the two netlisters AMS Designer offers.

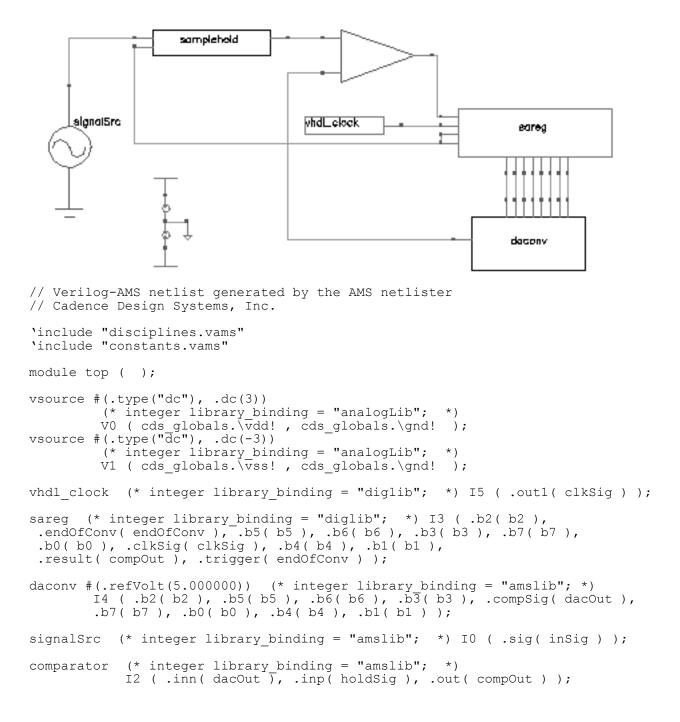

In this tutorial, you use the AMS Designer environment, the Spectre and UltraSim simulator solvers, SimVision, and (separately) the <code>amsdesigner</code> command to netlist, compile, elaborate, and simulate the <code>aeq\_ac\_sim</code> schematic which contains analog, digital, and mixed-signal components.

See the following topics for more information:

- <u>Setting Up the Tutorial</u> on page 30

- Running the Tutorial in the AMS Designer Environment on page 31

- Running the Tutorial Using the UltraSim Analog Solver on page 63

- Running the Tutorial from the Command Line on page 68

# **Setting Up the Tutorial**

To set up files and libraries for this tutorial, do the following:

**1.** Copy the tutorial files to your local working directory. For example:

```

mkdir myAMS

cd myAMS

cp -r $CDSHOME/tools/dfII/samples/AMS/vfs_amsflow/* .

```

**Note:** \$CDSHOME represents *your\_install\_dir*, the location of your Cadence Virtuoso<sup>®</sup> software installation. You must also have an environment variable, such as AMSHOME, that represents the location of your Cadence NC software installation. Your path must also contain the directories of the binary executables, such as virtuoso and ncsim.

2. Decompress and install the archive file:

```

gunzip vfs_amsflow.tar.gz

tar xf vfs_amsflow.tar

```

3. Change to the tutorial directory:

cd vfs\_amsflow

**4. Important**: Run the compilecms script in the tutorial files directory to compile the custom connect modules that this design uses so they are available for later use:

./compilecms

**Note:** In addition to compiling connect rules, this script also sets the TUTORHOME environment variable to the current directory:

setenv TUTORHOME `pwd`

## **Running the Tutorial in the AMS Designer Environment**

The tutorial design is a 6-bit, differential, flash, analog-to-digital converter (ADC) with a programmable analog equalizer filter on the front end and a 6-bit digital-to-analog converter (DAC) on the output. The output DAC reproduces the differential ADC input, providing a way to verify the behavior of the design. The hierarchy includes a mix of Verilog-A, Verilog (digital), VHDL-AMS, and schematic blocks.

In this part of the tutorial, you use the AMS Designer environment to specify simulation details, netlist, compile, elaborate, and simulate the tutorial design.

See the following topics for details:

- Opening the Schematic and Design Configuration on page 32

- Initializing AMS on page 37

- <u>Using the Quick Setup Form</u> on page 38

- <u>Using the Netlist and Run Form</u> on page 41

- Running the Simulation on page 57

- <u>Using the SimVision Source Browser</u> on page 60

- Using the SimVision Waveform Window on page 62

#### **Opening the Schematic and Design Configuration**

To open the top-level configuration and schematic of the tutorial design, do the following:

Show Me

1. Type virtuoso at the command line.

virtuoso &

The CIW appears.

|                                                                              | Virtuoso® 6.1.5 - Log: /home/arina/CDS.log |         |

|------------------------------------------------------------------------------|--------------------------------------------|---------|

| <u>F</u> ile <u>T</u> ools <u>O</u> ptions <u>H</u> elp                      |                                            | cādence |

| Loading vhdl.cxt<br>Loading seismic.cxt<br>Loading ci.cxt<br>Loading ams.cxt |                                            |         |

|                                                                              |                                            |         |

| mouse L:                                                                     | M:                                         | F       |

For more information on the CIW, see <u>"Using the Command Interpreter Window"</u> in the *Virtuoso Design Environment User Guide*.

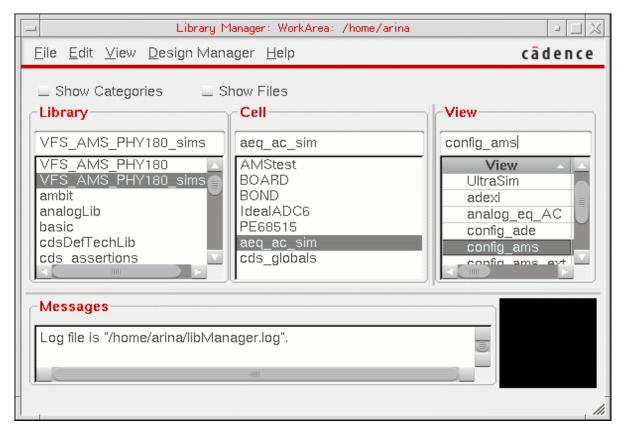

2. In the CIW, choose *Tools – Library Manager*.

The Library Manager window appears.

| Library Manager: WorkArea: /home/arina                             | x L +   |

|--------------------------------------------------------------------|---------|

| <u>File E</u> dit <u>V</u> iew <u>D</u> esign Manager <u>H</u> elp | cādence |

| Show Categories Show Files                                         |         |

| Messages                                                           |         |

| Log file is "/home/arina/libManager.log".                          |         |

|                                                                    | li.     |

- 3. In the *Library* column, click *VFS\_AMS\_PHY180\_sims* to view the cells in that library.

- 4. In the *Cell* column, click *aeq\_ac\_sim* to show all the views in that cell.

5. In the *View* column, double-click *config\_ams*.

The Open Configuration or Top CellView form appears.

6. In the *Open for editing* group box, select *yes* to open the configuration and *yes* to open the top cell view.

| -  | Open Configuration or Top CellView                        | N N         |

|----|-----------------------------------------------------------|-------------|

| ſ  | Open for editing                                          |             |

|    | Configuration "VFS_AMS_PHY180_sims aeq_ac_sim config_ams" | 🖲 yes 🥥 no  |

| Il | Top Cell View "VFS_AMS_PHY180_sims aeq_ac_sim schematic"  | 🖲 yes 🥥 no  |

|    | ОК                                                        | Cancel Help |

**7.** Click *OK*.

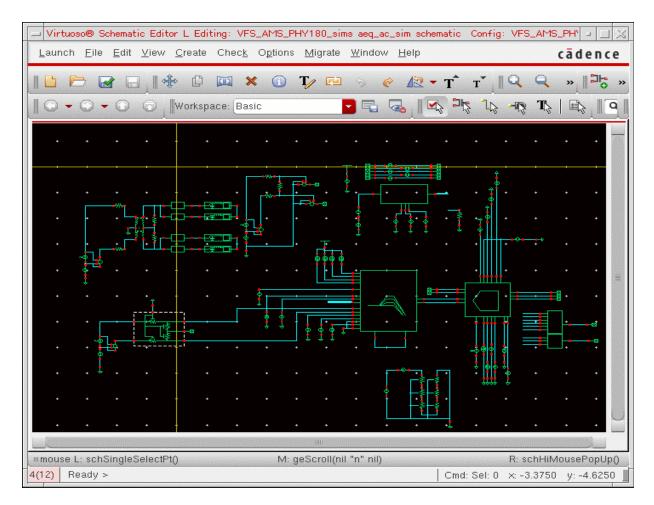

The  $aeq_ac_sim$  schematic view appears in the Virtuoso Schematic Editor and the  $aeq_ac_sim$  config view appears in the Virtuoso<sup>®</sup> Hierarchy Editor.

#### The *aeq\_ac\_sim* schematic looks like this:

| 🖃 Virtuoso® Hierarchy Editor: (VFS_AMS_PHV180_sims aeq_ac_sim config_ams) 💷 🖂 |                      |                                                      |                    |                     |          |    |

|-------------------------------------------------------------------------------|----------------------|------------------------------------------------------|--------------------|---------------------|----------|----|

| <u> </u>                                                                      | <u>H</u> elp         |                                                      |                    |                     | cādence  | e  |

| 🗅 🗁 🕞   🖓 🚸 א כ 🛈 📾 🖒   🖨 🎯                                                   |                      |                                                      |                    |                     |          |    |

| Top Cell                                                                      |                      | obal Bindings                                        | ur e               |                     | ? 8      | -  |

| Tub Cell                                                                      |                      | unai pinuinys                                        |                    |                     |          |    |

| Library: VFS_AMS_PHY18                                                        | 80_sims Libi         | Library List: HY180_sims basic analogLib GSCLib_20 ( |                    |                     | o_20 (   |    |

| Cell: aeq_ac_sim                                                              | Via                  | View List: Phavioral functional hdl schematic symbol |                    |                     |          | 1  |

|                                                                               |                      | w List: et                                           | iavioral functiona | a nai schematic syl |          |    |

| View: schematic                                                               | Sto                  | p List:                                              | ymbol              |                     | <u> </u> | )  |

|                                                                               |                      |                                                      |                    |                     |          |    |

| Open Edit                                                                     | Cor                  | nstraint List:                                       |                    |                     | (        | )  |

|                                                                               |                      |                                                      |                    |                     |          | _  |

| Table View Tree \                                                             | liou                 |                                                      |                    |                     |          |    |

| Cell Bindings                                                                 | VIEW                 |                                                      |                    |                     |          | ۱l |

| Cell Dinuings                                                                 |                      |                                                      |                    |                     |          |    |

| Library                                                                       | Cell                 | View Found                                           | 1 View To Use      | Inherited View      | List     |    |

| VFS_AMS_PHY180 AE                                                             | EQ_Dec               | behavioral                                           |                    | verilogams verilog  | ja b     |    |

| VFS_AMS_PHY180 AE                                                             | EQ_IvIshft_1p0_t     | schematic                                            |                    | verilogams verilog  | ja b     |    |

| VFS_AMS_PHY180 An                                                             | nalog_eq             | schematic                                            | schematic          | verilogams verilog  | ja b     |    |

| VFS_AMS_PHY180 An                                                             | nalog_eq_bias        | schematic                                            |                    | verilogams verilog  | ja b     |    |

| VFS_AMS_PHY180 An                                                             | nalog_eq_cmf         | schematic                                            |                    | verilogams verilog  | ja b     |    |

| VFS_AMS_PHY180 An                                                             | nalog_eq_gain        | schematic                                            |                    | verilogams verilog  | a b      |    |

| VFS_AMS_PHY180 An                                                             | nalog_eq_pcaps       | schematic                                            |                    | verilogams verilog  | ja b 🔍 🛛 |    |

|                                                                               | nalog_eq_pole        | schematic                                            |                    | verilogams verilog  | a b      |    |

| VFS_AMS_PHY180 ad                                                             | lc                   | verilogams                                           |                    | verilogams verilog  | a b      |    |

| VFS_AMS_PHY180 add                                                            | lc_64comparators     | verilogams                                           |                    | verilogams verilog  | a b      |    |

| VFS_AMS_PHY180 ad                                                             | Ic_IREF_ext          | verilogams                                           |                    | verilogams verilog  | a b      |    |

| VFS_AMS_PHY180 add                                                            | Ic_IREF_poly         | verilogams                                           |                    | verilogams verilog  | a b      |    |

|                                                                               | Ic_clk_nonoverlap    | schematic                                            | schematic          | verilogams verilog  | a b      |    |

|                                                                               | Ic_comparator_actr   | verilogams                                           |                    | verilogams verilog  |          |    |

|                                                                               | Ic_comparator_ar     | verilogams                                           |                    | verilogams verilog  |          |    |

|                                                                               | Ic_decode            | behavioral                                           | behavioral         | verilogams verilog  |          |    |

|                                                                               | _<br>lc_interp_array | verilogams                                           |                    | verilogams verilog  |          |    |

|                                                                               | Ic_interpolator      | verilogams                                           |                    | verilogams verilog  |          |    |

|                                                                               | lc_invertx1          | schematic                                            |                    | verilogams verilog  |          |    |

|                                                                               | _<br>lc_invertx10    | schematic                                            |                    | verilogams verilog  |          |    |

|                                                                               | _<br>lc_invertx100   | schematic                                            |                    | verilogams verilog  |          |    |

|                                                                               | _<br>lc_invertx3     | schematic                                            |                    | verilogams verilog  |          |    |

The *aeq\_ac\_sim* config view data looks like this:

## **Initializing AMS**

To install the AMS menu, specify a run directory, and specify the location of the hdl.var file that AMS Designer uses, do the following:

<u>Show Me</u>

**1.** In the Virtuoso<sup>®</sup> Hierarchy Editor, choose Plug-Ins - AMS.

AMS appears on the menu bar.

Virtuoso® Hierarchy Editor: (VFS\_AMS\_PHY180\_sims aeq\_ac\_sim config\_ams) <u>11</u>22 <u>File Edit View Plugins AMS Help</u> cādence

The *AMS* menu contains controls for the AMS Designer environment and simulator. When the *AMS* menu first appears, the only item you can select is *Initialize*.

2. Choose AMS – Initialize.

The AMS Initialize form appears.

3. Select New Run Directory.

The *New Run Directory* group box becomes active and the *Existing Run Directory* group box becomes inactive.

4. In the *Directory* field in the *New Run Directory* group box, type tutorial\_run.

|   |                                                        | AMS Initialize 🚽 🔀                    |  |

|---|--------------------------------------------------------|---------------------------------------|--|

| 1 | Design                                                 |                                       |  |

|   | Library                                                | VFS_AMS_PHY180_sims                   |  |

|   | Cell                                                   | aeq_ac_sim                            |  |

|   | View                                                   | config_ams                            |  |

|   |                                                        |                                       |  |

|   | 🔵 Existing Run I                                       | Directory 🧕 New Run Directory         |  |

|   | Existing Run Dir                                       | ectory                                |  |

|   | Directory /home/jillw/work/AMS/vfs_amsflow/test •      |                                       |  |

|   | New Run Directory                                      |                                       |  |

|   | Directory                                              | tutorial_run                          |  |

|   | Copy from existing run directory Import from ADE State |                                       |  |

| A | Nways use this r                                       | un directory for this configuration ⊻ |  |

|   |                                                        | OK Cancel Help                        |  |

- 5. (Optional) Mark the <u>Always use this run directory for this configuration</u> check box.

- **6.** Click *OK*.

Note: Other items on the AMS menu become active.

## **Using the Quick Setup Form**

You can use the Quick Setup form for AMS if you already have files that specify your simulation setup information, such as a simulation control file, a Tcl input script, or an hdl.var file. In the case of this tutorial, we have a Tcl script (demo.tcl) and an hdl.var file containing setup information. To specify these files, do the following:

Show Me

**1.** In the Virtuoso<sup>®</sup> Hierarchy Editor, choose *AMS – Quick Setup*.

The Quick Setup form appears.

| -                       | ams1: Quick Setup 💷 🖂                |

|-------------------------|--------------------------------------|

| Analog solver           | 🖲 Spectre 🥥 UltraSim 🥥 APS           |

| Waveform viewer         | SimVision 	Usualization and Analysis |

| Simulation control file | [ Edit                               |

| Tcl input script        | Edit                                 |

| hdl.var file            | (Edit)                               |

|                         | OK Cancel Defaults Apply Help        |

- 2. To the right of the *Tcl input script* field, click the browse button.

- **3.** On the Choose form that appears, double-click demo.tcl in the vfs\_amsflow directory.

The full path to demo.tcl appears in the *Tcl input script* field on the Quick Setup form.

|                         | ams1: Quick Setup 💷 🖂                            |

|-------------------------|--------------------------------------------------|

| Analog solver           | 💌 Spectre 🥥 UltraSim 🥥 APS                       |

| Waveform viewer         | SimVision 	Usualization and Analysis             |

| Simulation control file | Edit)                                            |

| TcI input script        | <pre>iome/arina/vfs_amsflow/demo.tcll Edit</pre> |

| hdl.var file            | Edit)                                            |

|                         | OK Cancel Defaults Apply Help                    |

This Tcl script contains the following commands:

```

set display_unit NS

set time_unit module

alias tp run -timepoint

alias . run

alias quit exit

stop -time 50ns -absolute

```

4. To the right of the *hdl.var file* field on the Quick Setup form, click the browse button.

5. On the Choose form that appears, double-click hdl.var in the vfs\_amsflow directory.

This hdl.var file appears in the hdl.var file field on the Quick Setup form.

|                         | ams1: Quick Setup 💷 🖂                    |

|-------------------------|------------------------------------------|

| Analog solver           | 🖲 Spectre 🥥 UltraSim 🥥 APS               |

| Waveform viewer         | 🖲 SimVision 🧉 Visualization and Analysis |

| Simulation control file | Edit)                                    |

| Tcl input script        | 1ome/arina/vfs_amsflow/demo.tcl Edit     |

| hdl.var file            | home/arina/vfs_amsflow/hdl.var           |

| -                       | OK Cancel Defaults Apply Help            |

This hdl.var file contains the following definitions:

define ncuse5x define ncvlogopts -linedebug -mess -define SPEEDUP -nowarn MACNDF -nowarn RECOMP define ncelabopts -nowarn CUVWSP -nowarn CUNGL1 -nowarn CSINFI -nowarn CUVUKP -nowarn CUSRCH -nowarn SYWARN define ncvhdlopts -linedebug -mess -v93

6. Click OK.

## Using the Netlist and Run Form

You can use the Netlist and Run form to specify the following details prior to <u>running the AMS</u> <u>Designer simulator with the Spectre solver</u> and using the SimVision waveform viewer:

- <u>Transient stop time</u>

- Model file for simuation

- Verilog-AMS include file search path

- <u>Outputs</u> you want to save and plot

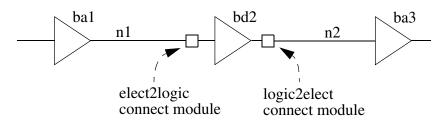

- Connect rules

- Netlist and run options

**Note:** You can also specify these most of these details using the *AMS – Detailed Setup* pull-right menu choices as follows:

| Transient stop time       | Choose AMS – Detailed Setup – Analyses          |

|---------------------------|-------------------------------------------------|

| Model file for simulation | Choose AMS – Detailed Setup – Model Libraries   |

| Verilog-AMS include file  | Choose AMS – Detailed Setup – AMS Options       |

| Outputs to save and plot  | Choose AMS – Detailed Setup – Save/Plot Outputs |

| Connect rules             | Choose AMS – Detailed Setup – Connect Rules     |

To open the Netlist and Run form, do the following:

► In the Virtuoso<sup>®</sup> Hierarchy Editor, choose *AMS* – *Netlist and Run*.

The Netlist and Run form appears.

| ams0: Netlist and Run: VFS_AMS_PH                                                                                                                                                                | Y180_sims aeq_ac_sim config_ams 🔄 🔀        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|

| RUN DIRECTORY<br>/home/jillw/work/AMS/IC613/chap2/vfs_amsflow/tutorial_run                                                                                                                       |                                            |  |

| NETLIST AND RUN MODE<br>© OSS-based netlister with irun<br>• Cellview-based netlister with novlog, noelab, no                                                                                    | csim                                       |  |

| RUN OPTIONS       SIMULATION OPTIONS         ✓ Netlist incremental       All         ✓ Compile incremental       All         ✓ Elaborate incremental       All         ✓ Simulate       Simulate |                                            |  |

| CONNECT RULES<br>Library connectLib Cell ConnRules_                                                                                                                                              | 25V_mid View connect<br>Connect Rules Form |  |

| GLOBAL DESIGN DATA MODULE<br>Library AMS_PHY180_sims Cell cds_global<br>SIMULATION SNAPSHOT                                                                                                      |                                            |  |

| Library AMS_PHY180_sims Cell aeq_ac_sim<br>HOST MODE<br>Host • Local © Remote © Distributed<br>Remote host Job submission stri                                                                   |                                            |  |

#### Specifying the Transient Stop Time

To specify the transient stop time for the analog solver, do the following:

➤ On the <u>Netlist and Run form</u>, in the *SIMULATION OPTIONS* group box, in the *Transient stop time* field, type 100n.

| SIMULATION OPTIONS  |                   |  |  |  |  |

|---------------------|-------------------|--|--|--|--|

| Transient stop time | 100n              |  |  |  |  |

| Model Libraries     | Options Save/Plot |  |  |  |  |

| Simulate GUI        |                   |  |  |  |  |

**Note:** You can specify additional analysis settings by choosing *AMS – Detailed Setup*. For details, see <u>Chapter 4, "Using the Detailed Setup Menu."</u>

#### **Specifying the Simulation Model File**

To specify the simulation model file, do the following:

<u>Show Me</u>

1. On the <u>Netlist and Run form</u>, in the *SIMULATION OPTIONS* group box, click *Model Libraries*.

| SIMULATION OPTIONS  |                   |  |  |  |

|---------------------|-------------------|--|--|--|

| Transient stop time | 100n              |  |  |  |

| Model Libraries     | Options Save/Plot |  |  |  |

| Simulate GUI        |                   |  |  |  |

The Model Library Setup form appears.

|   | - ar                                                                                | ns1: Model Library Setup    |              | L<br>X |

|---|-------------------------------------------------------------------------------------|-----------------------------|--------------|--------|

|   | ⊡- Global Model Files<br>I [[ <click add="" file="" here="" model="" to=""></click> | Model File<br>Browse button | Section      |        |

| 1 |                                                                                     | Сок                         | Cancel Apply | Help   |

- **2.** Click the browse button.

- **3.** On the Choose form that appears, navigate to and double-click the vfs\_amsflow/ spectre\_models/gpdk.scs file.

This model file appears in the *Global Model Files* tree on the <u>Model Library Setup form</u>.

| ams1: Model Library Setup                                                                                                                                                        | N L X |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Model File     Section       □     Global Model Files       □        ✓     /home/jillw/work/AMS/vfs_amsflow/spectre_models/gpdk.scs       □        Click here to add model file> |       |

| OK Cancel Apply                                                                                                                                                                  |       |

4. In the drop-down combo box in the Section column, select NN.

NN specifies the model designed to represent nominal operating conditions.

| _  | ams1: Model Library Setup                                                                                                                                                                          |                                                      | □ □    | $\mathbb{X}$ |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------|--------------|

|    | Model File<br>- Global Model Files<br>✓ /home/jillw/work/AMS/vfs_amsflow/spectre_models/gpdk.scs<br>– </th <th>Section<br/>NN<br/>SS<br/>SF<br/>FS<br/>FF<br/>Edit button</th> <th></th> <th></th> | Section<br>NN<br>SS<br>SF<br>FS<br>FF<br>Edit button |        |              |

| Ι. |                                                                                                                                                                                                    | OK Cancel Apply                                      | )(Help |              |

5. (Optional) Click the edit button.

The model file appears in an editing window so you can see which files will contribute to the characterization of the various operating conditions.

| /home/jillw/work/AMS/vfs_amsflow/spectre_models/gpdk.scs                                                                                                                                                                                                                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPDK Corner Definitions<br>* This is an example file showing how to define corners<br>* using model files for individual components as the<br>* building blocks.                                                                                                                            |  |

| simulator lang=spectre<br>global 0 VDD VSS DVDD                                                                                                                                                                                                                                             |  |

| library gpdk                                                                                                                                                                                                                                                                                |  |

| section NN<br>include "mos25gen.scs" section=tt<br>include "nmos1.scs" section=nom<br>include "pmos1.scs" section=nom<br>include "resistor.scs" section=res<br>include "capacitor.scs" section=cap<br>include "diode.scs" section=dio<br>include "bipolar.scs" section=bjt<br>endsection NN |  |

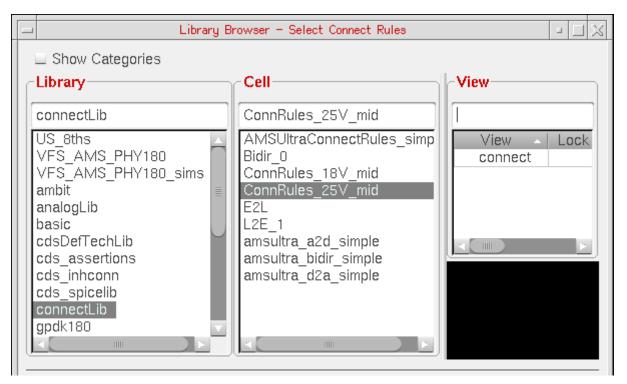

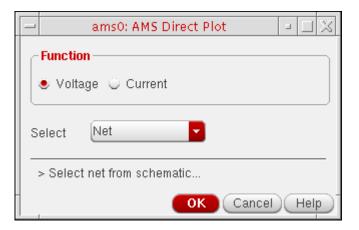

| section SS<br>include "mos25gen.scs" section=ss<br>include "nmos1.scs" section=slow                                                                                                                                                                                                         |  |