# Virtuoso<sup>®</sup> Spectre<sup>®</sup> Circuit Simulator and Accelerated Parallel Simulator User Guide

Product Version 13.1.1 April 2014 © 2003–2014 Cadence Design Systems, Inc. All rights reserved.

Printed in the United States of America.

Cadence Design Systems, Inc. (Cadence), 2655 Seely Ave., San Jose, CA 95134, USA.

MMSIM contains technology licensed from, and copyrighted by: C. L. Lawson, R. J. Hanson, D. Kincaid, and F. T. Krogh © 1979, J. J. Dongarra, J. Du Croz, S. Hammarling, and R. J. Hanson © 1988, J. J. Dongarra, J. Du Croz, I. S. Duff, and S. Hammarling © 1990; University of Tennessee, Knoxville, TN and Oak Ridge National Laboratory, Oak Ridge, TN © 1992-1996; Brian Paul © 1999-2003; M. G. Johnson, Brisbane, Queensland, Australia © 1994; Kenneth S. Kundert and the University of California, 1111 Franklin St., Oakland, CA 94607-5200 © 1985-1988; Hewlett-Packard Company, 3000 Hanover Street, Palo Alto, CA 94304-1185 USA © 1994, Silicon Graphics Computer Systems, Inc., 1140 E. Arques Ave., Sunnyvale, CA 94085 © 1996-1997, Moscow Center for SPARC Technology, Moscow, Russia © 1997; Regents of the University of California, 1111 Franklin St., Oakland, CA 94607-5200 © 1990-1994, Sun Microsystems, Inc., 4150 Network Circle Santa Clara, CA 95054 USA © 1994-2000, Scriptics Corporation, and other parties © 1998-1999; Aladdin Enterprises, 35 Efal St., Kiryat Arye, Petach Tikva, Israel 49511 © 1999 and Jean-loup Gailly and Mark Adler © 1995-2005; RSA Security, Inc., 174 Middlesex Turnpike Bedford, MA 01730 © 2005.

All rights reserved. Associated third party license terms may be found at <install dir>/doc/OpenSource/\*

Open SystemC, Open SystemC Initiative, OSCI, SystemC, and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission.

**Trademarks**: Trademarks and service marks of Cadence Design Systems, Inc. contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 800.862.4522. All other trademarks are the property of their respective holders.

**Restricted Permission:** This publication is protected by copyright law and international treaties and contains trade secrets and proprietary information owned by Cadence. Unauthorized reproduction or distribution of this publication, or any portion of it, may result in civil and criminal penalties. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. Unless otherwise agreed to by Cadence in writing, this statement grants Cadence customers permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used only in accordance with a written agreement between Cadence and its customer.

- 2. The publication may not be modified in any way.

- 3. Any authorized copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement.

- 4. The information contained in this document cannot be used in the development of like products or software, whether for internal or external use, and shall not be used for the benefit of any other party, whether or not for consideration.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor

## **Contents**

| Preface                                            | 19 |

|----------------------------------------------------|----|

| <u>Licensing</u>                                   |    |

| License Checkout Order                             |    |

| Lock Feature Licenses                              |    |

| Using License Queuing                              |    |

| Suspending and Resuming Licenses                   |    |

| Related Documents for Spectre                      |    |

| Third Party Tools                                  |    |

| Typographic and Syntax Conventions                 |    |

| References                                         |    |

|                                                    |    |

| 1                                                  |    |

|                                                    |    |

| Introducing the Virtuoso Spectre Circuit Simulator |    |

| Improvements over SPICE                            |    |

| Improved Capacity                                  |    |

| Improved Accuracy                                  |    |

| Improved Speed                                     | 30 |

| Improved Reliability                               |    |

| Improved Models                                    |    |

| Spectre Usability Features and Customer Service    |    |

| Analog HDL                                         | 32 |

| AHDL Linter                                        |    |

| RF Capabilities                                    | 34 |

| Periodic Analysis                                  | 34 |

| Quasi-Periodic Analysis                            | 34 |

| Envelope Analysis                                  | 35 |

| Harmonic Balance Steady State Analysis (HB)        | 36 |

| Spectre Accelerated Parallel Simulator             | 36 |

| Starting APS Simulations                           | 36 |

| Specifying Multi-Threading Options                 | 37 |

| Using the cktpreset=sampled option                 | 38 |

| Additional Notes                                                           |

|----------------------------------------------------------------------------|

| APS Distributed Mode                                                       |

| Simulation Diagnostics 40                                                  |

| Spectre eXtensive Partitioning Simulator                                   |

| Starting an XPS Simulation41                                               |

| Post-layout Simulation                                                     |

| Dynamic Current and Power Simulation42                                     |

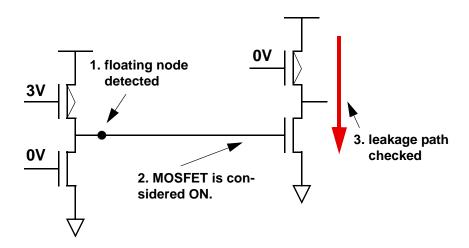

| Leakage Current and Power Simulation42                                     |

| XPS Variation Analysis                                                     |

| Supported Spectre Options and Features44                                   |

| Unsupported Spectre Options and Features44                                 |

| Known Issues and Limitations44                                             |

| Spectre XPS SPICE Mode45                                                   |

| Starting an XPS SPICE Mode Timing Simulation45                             |

| Starting an XPS SPICE Mode Dynamic Power/Leakage Simulation 45             |

| <u>Environments</u>                                                        |

| <u>2</u><br>Getting Started with the Virtuoso Spectre Circuit Simulator 47 |

| Jsing the Example and Displaying Results48                                 |

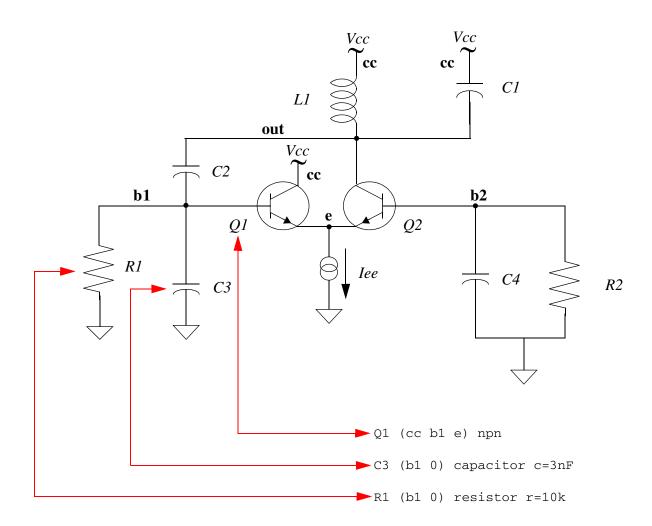

| Sample Schematic                                                           |

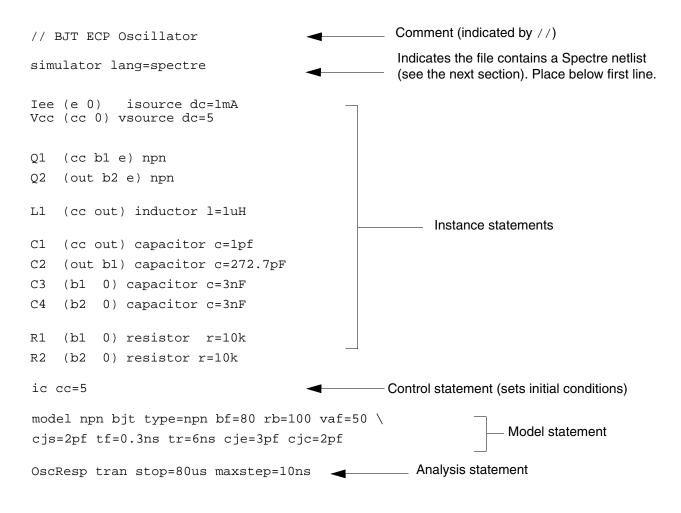

| <br><u>Sample Netlist</u>                                                  |

| Elements of a Spectre Netlist50                                            |

| nstructions for a Spectre Simulation Run54                                 |

| Following Simulation Progress54                                            |

| Screen Printout                                                            |

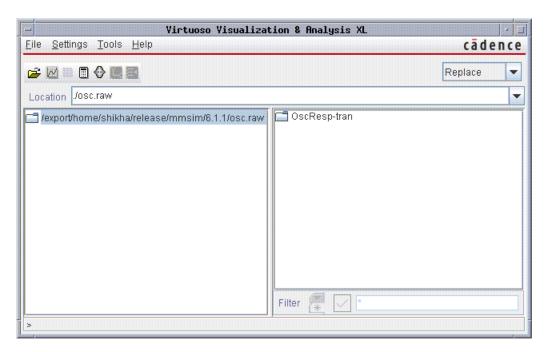

| <u> Viewing Your Output</u> 56                                             |

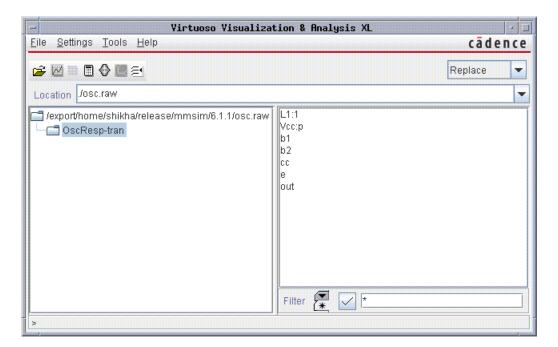

| Starting Virtuoso Visualization and Analysis XL56                          |

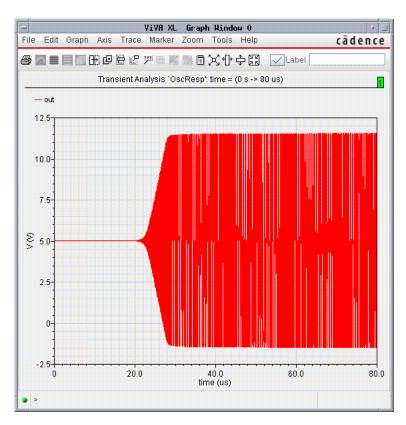

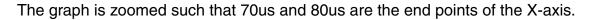

| Plotting Signals 57                                                        |

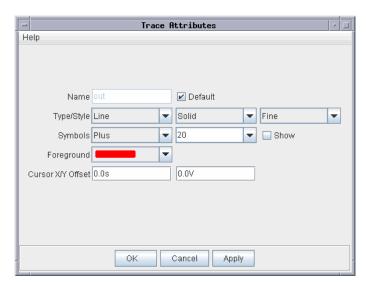

| Changing the Trace Color 60                                                |

| Learning More about Virtuoso Visualization and Analysis XL                 |

|                                                                            |

| _                                                                          |

| <u>3</u>                                                                   |

| <u>3</u><br>SPICE Compatibility63                                          |

| PSpice Netlist and Device Model Support           |

|---------------------------------------------------|

| <u>4</u>                                          |

| Spectre Netlists 67                               |

| •                                                 |

| Netlist Statements                                |

| Netlist Conventions                               |

| Basic Syntax Rules                                |

| Spectre Language Modes                            |

| Creating Component and Node Names 70              |

| Escaping Special Characters in Names              |

| <u>Duplicate Specification of Parameters</u>      |

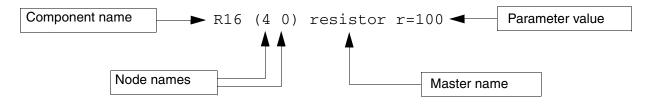

| <u>Instance Statements</u>                        |

| Formatting the Instance Statement                 |

| Examples of Instance Statements                   |

| Basic Instance Statement Rules                    |

| Identical Components or Subcircuits in Parallel   |

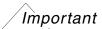

| Analysis Statements                               |

| Basic Formatting of Analysis Statements           |

| Examples of Analysis Statements78                 |

| Basic Analysis Rules                              |

| Control Statements                                |

| Formatting the Control Statement 80               |

| Examples of Control Statements 80                 |

| <u>Model Statements</u>                           |

| Formatting the model Statement82                  |

| Creating a Model Alias                            |

| Creating an alias for a Subcircuit                |

| Examples of model Statements                      |

| Using analogmodel for Model Passing (analogmodel) |

| Basic model Statement Rules                       |

| Input Data from Multiple Files                    |

| Syntax for Including Files                        |

| Formatting the include Statement                  |

| Rules for Using the include Statement             |

| Example of include Statement Use 89               |

| Reading Piecewise Linear (PWL) Vector Values from a File Using Library Statements  Multidisciplinary Modeling Setting Tolerances with the quantity Statement Inherited Connections |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| <u>5</u>                                                                                                                                                                           |             |

| Parameter Specification and Modeling Features                                                                                                                                      | <u>3</u> 95 |

| Instance (Component or Analysis) Parameters                                                                                                                                        | 96          |

| Types of Parameter Values                                                                                                                                                          |             |

| Parameter Dimension                                                                                                                                                                | 96          |

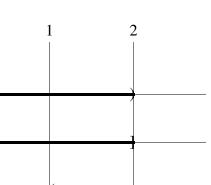

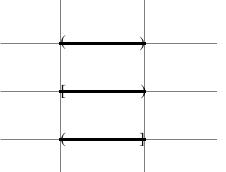

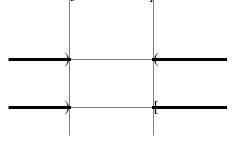

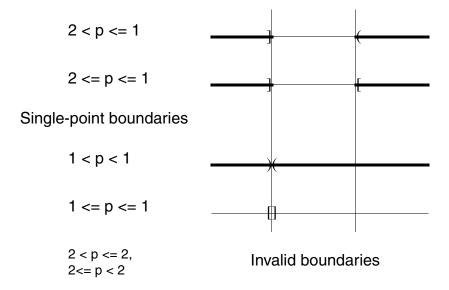

| Parameter Ranges                                                                                                                                                                   | 97          |

| Help on Parameters                                                                                                                                                                 | 98          |

| Scaling Numerical Literals                                                                                                                                                         | 99          |

| Parameters Statement                                                                                                                                                               | 100         |

| Circuit and Subcircuit Parameters                                                                                                                                                  | 101         |

| Parameter Declaration                                                                                                                                                              | 101         |

| Parameter Inheritance                                                                                                                                                              |             |

| Parameter Referencing                                                                                                                                                              | 102         |

| Altering/Sweeping Parameters                                                                                                                                                       | 102         |

| Expressions                                                                                                                                                                        | 102         |

| Behavioral Expressions                                                                                                                                                             | 106         |

| Built-in Constants                                                                                                                                                                 |             |

| <u>User-Defined Functions</u>                                                                                                                                                      | 113         |

| Predefined Netlist Parameters                                                                                                                                                      | 114         |

| <u>Subcircuits</u>                                                                                                                                                                 | 114         |

| Formatting Subcircuit Definitions                                                                                                                                                  | 115         |

| A Subcircuit Definition Example                                                                                                                                                    | 116         |

| Subcircuit Example                                                                                                                                                                 | 116         |

| Rules to Remember                                                                                                                                                                  | 117         |

| Calling Subcircuits                                                                                                                                                                |             |

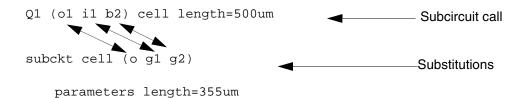

| Modifying Subcircuit Parameter Values                                                                                                                                              | 119         |

| Checking for Invalid Parameter Values                                                                                                                                              | 119         |

| Conditional Subcircuits                                                                                                                                                            | 120         |

| Inline Subcircuits                                                                                                                                                                 |             |

| Modeling Parasitics                                                        |     |

|----------------------------------------------------------------------------|-----|

| Parameterized Models                                                       |     |

| Inline Subcircuits Containing Only Inline model Statements                 |     |

| Process Modeling Using Inline Subcircuits                                  |     |

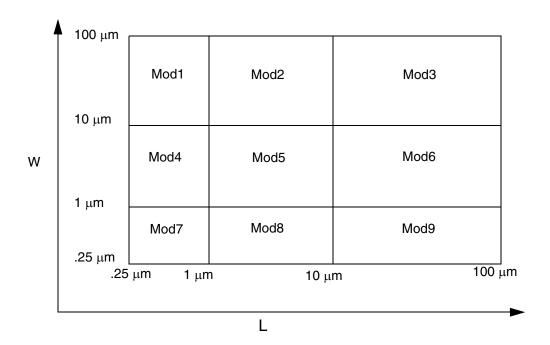

| Binning                                                                    | 128 |

| Auto Model Selection                                                       | 130 |

| Conditional Instances                                                      | 131 |

| Scaling Physical Dimensions of Components and Device Model Technology      | 141 |

| Multi-Technology Simulation                                                | 143 |

| <u>6</u>                                                                   |     |

| Modeling for Signal Integrity                                              | 145 |

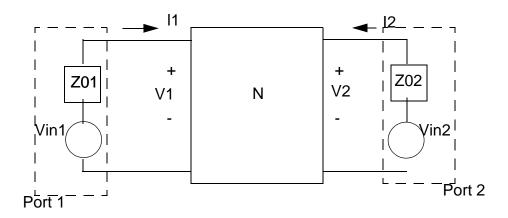

| N-Port Modeling                                                            |     |

| N-Port Example                                                             | 146 |

| Creating an S-Parameter File Automatically                                 |     |

| Creating an S, Y, or Z-Parameter File Manually                             |     |

| Reading the S, Y or Z-Parameter File                                       |     |

| Improving the Modeling Capability of the N-Port                            |     |

| S-Parameter File Format Translator                                         |     |

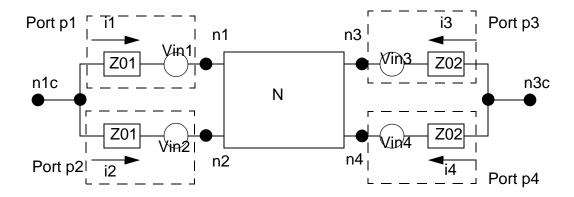

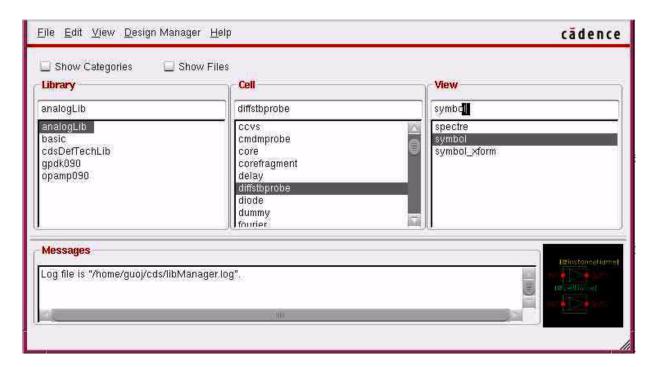

| Standard Scattering Parameter Modeling and Mixed-Mode Scattering Parameter |     |

| Modeling                                                                   | 153 |

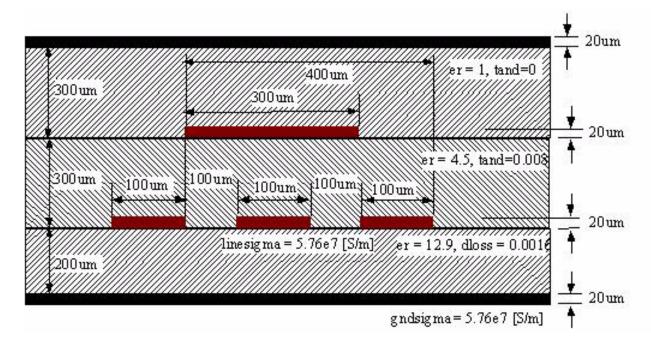

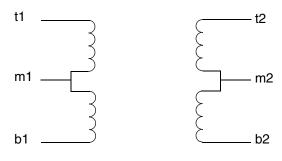

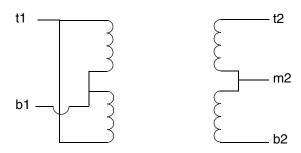

| Transmission Line Modeling                                                 | 159 |

| Constant RLGC Matrices                                                     | 160 |

| Frequency-Dependent RLGC Data                                              | 161 |

| 2-D Field Solver Geometry and Material Information                         |     |

| S-Parameter Data                                                           |     |

| TLINE Parameters                                                           |     |

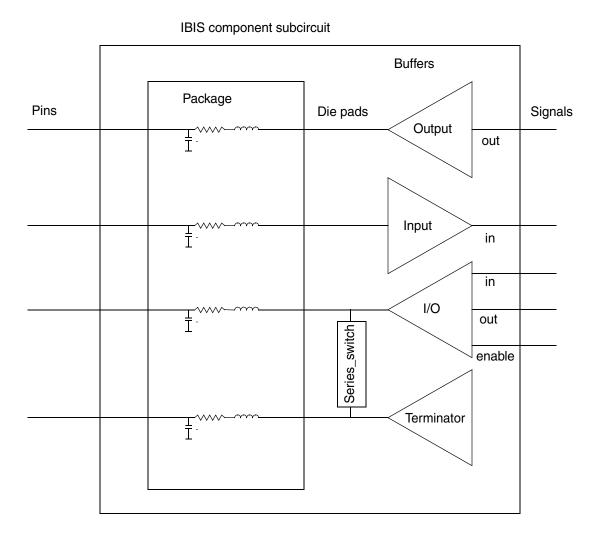

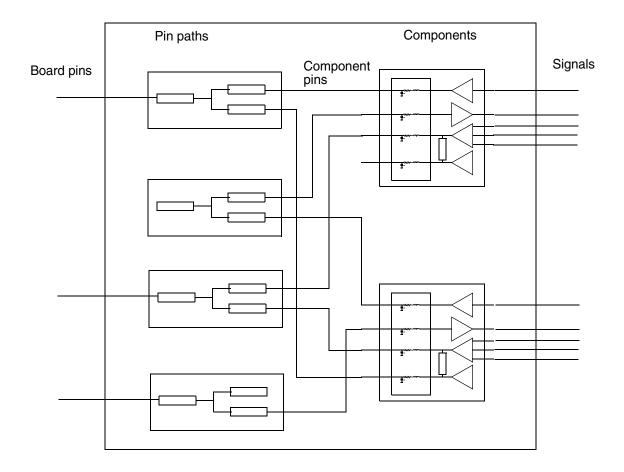

| Input/Output Buffer Modeling Using IBIS                                    | 166 |

| IBIS Translator Model                                                      |     |

| Example of an IBIS Component Subcircuit                                    |     |

| <u>7</u>                                                                   |     |

|                                                                            |     |

| <u>Analyses</u>                                                            | 171 |

| Types of Analyses                                                          | 172 |

| Analysis Parameters                                                        | 174 |

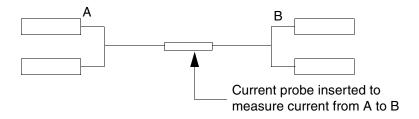

| Probes in Analyses                                           |    |

|--------------------------------------------------------------|----|

| Multiple Analyses                                            | 76 |

| Multiple Analyses in a Subcircuit                            | 78 |

| Example17                                                    | 78 |

| <u>DC Analysis</u>                                           | 79 |

| Selecting a Continuation Method18                            |    |

| Enabling Fast DC Simulation18                                | 81 |

| AC Analysis                                                  | 82 |

| Transient Analysis                                           | 83 |

| Sweeping Parameters During Transient Analysis18              | 83 |

| Balancing Accuracy and Speed18                               | 85 |

| The errpreset Parameter18                                    | 85 |

| Setting the Integration Method18                             | 88 |

| Improving Transient Analysis Convergence18                   | 89 |

| Controlling the Amount of Output Data                        | 89 |

| Calculating Transient Noise                                  | 94 |

| Performing Small-Signal Analyses during a Transient Analysis | 95 |

| Generating EMIR Output During Transient Analysis             | 96 |

| Pole Zero Analysis                                           | 97 |

| <u>Syntax</u>                                                | 97 |

| <u>Example 1</u>                                             | 98 |

| <u>Example 2</u>                                             | 98 |

| <u>Example 3</u>                                             | 98 |

| Example 4                                                    | 98 |

| Output Log File                                              | 98 |

| Other Analyses (sens, fourier, dcmatch, and stb)             | 99 |

| Sensitivity Analysis                                         |    |

| Fourier Analysis                                             |    |

| DC Match Analysis                                            |    |

| Stability Analysis                                           | 11 |

| Advanced Analyses (sweep and montecarlo)2                    |    |

| Sweep Analysis                                               |    |

| Monte Carlo Analysis                                         |    |

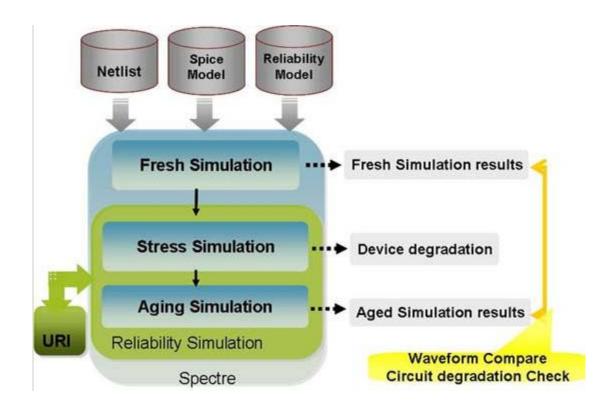

| Spectre Reliability Analysis                                 |    |

| Reliability Simulation Block                                 |    |

| Reliability Control Statements Reference                     |    |

| accuracy (*relxpert: accuracy)                          | 239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| age (*relxpert: age)                                    | 240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| agelevel_only ( *relxpert: agelevel_only )              | 241                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| degsort (*relxpert: degsort)                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| deltad (*relxpert: deltad)                              | 243                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| dumpagemodel (*relxpert: dumpagemodel)                  | 244                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| enablenativeage (*relxpert enable negative age)         | 245                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| gradual_aging_agepoint (*relxpert: agepoint)            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| gradual_aging_agestep (*relxpert: agestep)              | 247                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| idmethod (*relxpert: idmethod)                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| igatemethod (*relxpert: igatemethod)                    | 250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| maskdev ( *relxpert: maskdev )                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| minage (*relxpert: minage)                              | 253                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| output op degrad                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| relx tran ( *relxpert: relx tran )                      | 257                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| · · · ·                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| simmode                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| a satural. Otata sa a sata                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ontrol Statements                                       | 263                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| e alter and altergroup Statements                       | 264                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Changing Parameter Values for Components                | 264                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Changing Parameter Values for Models                    | 265                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Further Examples of Changing Component Parameter Values | 265                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Changing Parameter Values for Circuits                  | 266                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| e ic and nodeset Statements                             | 266                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Setting Initial Conditions for All Transient Analyses   | 267                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Supplying Solution Estimates to Increase Speed          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Specifying State Information for Individual Analyses    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (                                                       | agelevel_only (*relxpert: agelevel_only) degsort (*relxpert: degsort) deltad (*relxpert: deltad) dumpagemodel (*relxpert: dumpagemodel) enablenativeage (*relxpert enable negative age) gradual_aging_agepoint (*relxpert: agestep) idmethod (agestep (*relxpert: agestep) idmethod (*relxpert: idmethod) igatemethod (*relxpert: igatemethod) isubmethod (*relxpert: isubmethod) maskdev (*relxpert: maskdev) minage (*relxpert: minage) opmethod (*relxpert: opmethod) reset analysis param output_op_degrad rek_tran (*relxpert: relx_tran) report model param (*relxpert: report model param) simmode uri_lib (*relxpert: uri_lib) User-Defined Reliability Models Measuring the Reliability Analysis  changing Parameter Values for Components Changing Parameter Values for Component Parameter Values Changing Parameter Values for Circuits e ic and nodeset Statements Setting Initial Conditions for All Transient Analyses Supplying Solution Estimates to Increase Speed |

| The info Statement                                             | 271 |

|----------------------------------------------------------------|-----|

| Specifying the Parameters You Want to Save                     | 272 |

| Specifying the Output Destination                              | 273 |

| Examples of the info Statement                                 |     |

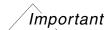

| Printing the Node Capacitance Table                            | 274 |

| The options Statement                                          |     |

| options Statement Format                                       | 279 |

| options Statement Example                                      | 279 |

| Performing Parasitic Reduction                                 | 279 |

| Setting Tolerances                                             |     |

| Specifying Hierarchical Delimiters                             | 280 |

| Additional options Statement Settings You Might Need to Adjust |     |

| Simulation Config file Support                                 |     |

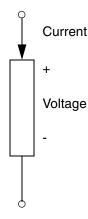

| Computing the Constant Current                                 | 282 |

| The paramset Statement                                         |     |

| The save Statement                                             | 283 |

| Saving Signals for Individual Nodes and Components             | 284 |

| Saving Groups of Signals                                       |     |

| Using Wildcards in the Save Statement                          |     |

| The print Statement                                            |     |

| <u>Examples</u>                                                | 298 |

| The set Statement                                              | 298 |

| The shell Statement                                            | 299 |

| The statistics Statement                                       |     |

|                                                                |     |

| 9                                                              |     |

|                                                                | 004 |

| Specifying Output Options                                      | 301 |

| Signals as Output                                              | 302 |

| Saving all AHDL Variables                                      | 302 |

| Listing Parameter Values as Output                             | 302 |

| Specifying the Parameters You Want to Save                     | 303 |

| Specifying the Output Destination                              | 304 |

| Examples of the info Statement                                 | 304 |

| Preparing Output for Viewing                                   | 304 |

| Output Formats Supported by the Spectre Simulator              | 304 |

| Defining Output File Formats                                             |     |

|--------------------------------------------------------------------------|-----|

| Accessing Output Files                                                   |     |

| How the Spectre Simulator Creates Names for Output Directories and Files |     |

| Filenames for SPICE Input Files                                          | 309 |

| Specifying Your Own Names for Directories                                | 309 |

| <u>10</u>                                                                |     |

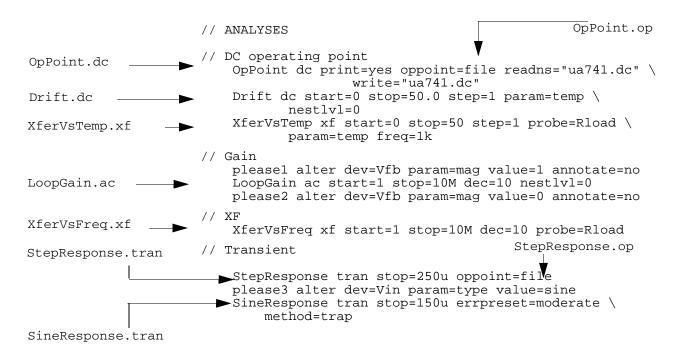

| Running a Simulation                                                     | 311 |

| Running Spectre in 64-Bit                                                | 312 |

| Starting Simulations                                                     |     |

| Specifying Simulation Options                                            |     |

| Using License Queuing                                                    |     |

| Suspending and Resuming Licenses                                         |     |

| Determining Whether a Simulation Was Successful                          |     |

| Checking Simulation Status                                               | 315 |

| Interrupting a Simulation                                                | 316 |

| Recovering from Transient Analysis Terminations                          | 316 |

| Creating Saved State Files                                               | 316 |

| Creating checkpoint Files                                                | 318 |

| Creating Recovery Files from the Command Line                            | 319 |

| Setting Recovery File Specifications for a Single Analysis               | 319 |

| Restarting a Transient Analysis                                          | 319 |

| Output Directory after Recovery                                          | 320 |

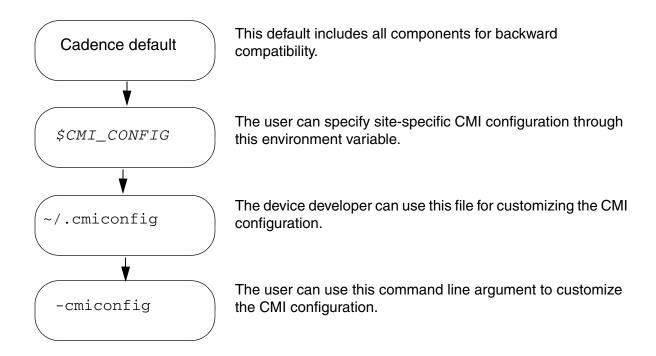

| Controlling Command Line Defaults                                        | 320 |

| Examining the Spectre Simulator Defaults                                 | 320 |

| Setting Your Own Defaults                                                |     |

| References for Additional Information about Specific Defaults            |     |

| Overriding Defaults                                                      | 322 |

| 11                                                                       |     |

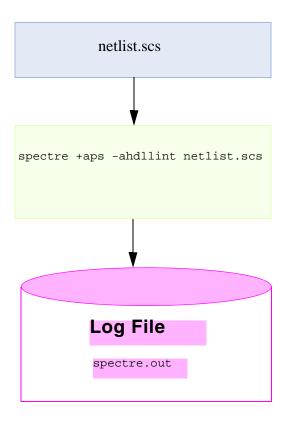

| AHDL Linter Checks                                                       | 323 |

| About the AHDL Linter Feature                                            |     |

| Using the AHDL Linter Feature in APS                                     |     |

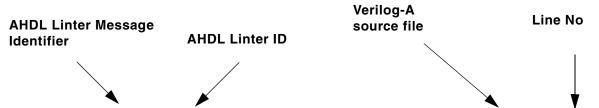

| Identifying AHDL Linter Messages                                         |     |

| Static AHDL Linter Message                                               |     |

| Dynamic AHDL Linter Message  Filtering AHDL Linter Messages  Using the ahdlhelp Utility | 327 |

|-----------------------------------------------------------------------------------------|-----|

| <u>12</u>                                                                               |     |

| Device and Circuit Checks                                                               | 329 |

| Device Checks                                                                           |     |

| The assert Statement                                                                    |     |

| The check Statement                                                                     |     |

| The checklimit Statement                                                                |     |

| Format of Violations in the .violations File                                            |     |

| Circuit Checks                                                                          |     |

| Circuit Check Scoping                                                                   |     |

| Output Format                                                                           |     |

| Circuit Check SpiceVision PRO Integration                                               |     |

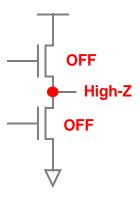

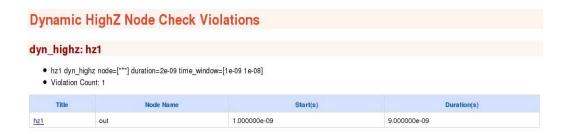

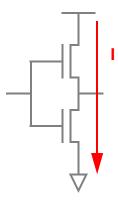

| Dynamic Checks                                                                          |     |

| Static Checks                                                                           |     |

| 13 Post-Layout Simulation                                                               | 419 |

| Parasitic Reduction                                                                     | 420 |

| EMIR Analysis                                                                           | 420 |

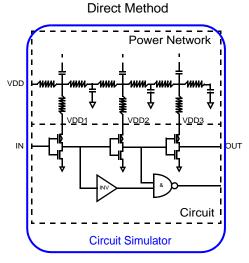

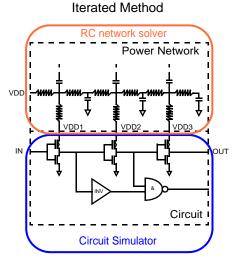

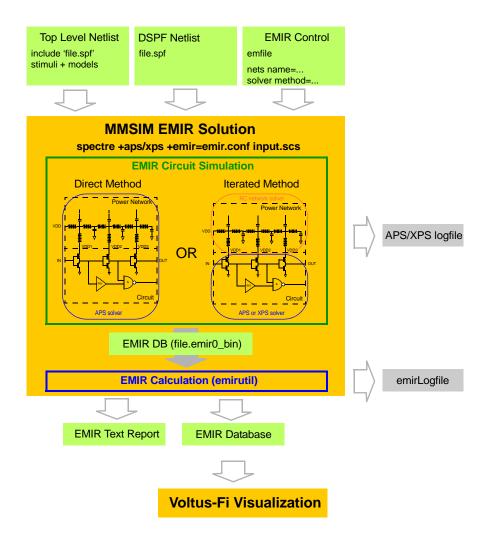

| Spectre APS/XPS EMIR Flow Overview                                                      | 421 |

| EMIR Flow Setup                                                                         |     |

| EMIR Results                                                                            | 433 |

| SPEF Netlist Support                                                                    | 434 |

| Signal Net IR Drop                                                                      | 434 |

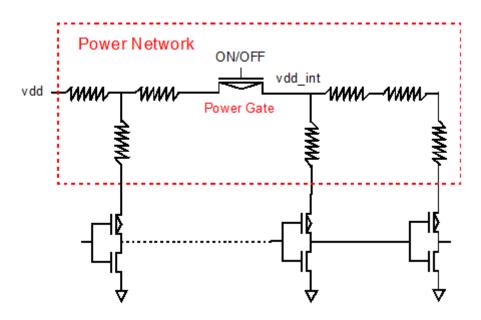

| Power Gate Support                                                                      | 435 |

| Temperature Handling                                                                    | 436 |

| Port Order Handling                                                                     | 437 |

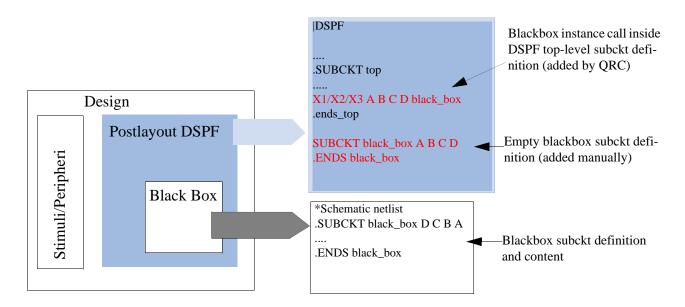

| Blackbox Handling                                                                       | 440 |

| Comparing the Direct And Iterated Method EMIR Results                                   | 440 |

| SPF Checker                                                                             | 442 |

| Other Features                                                                          | 443 |

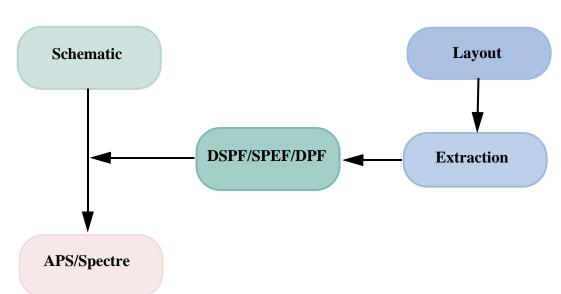

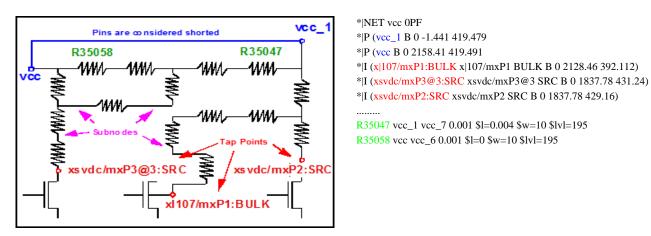

| APS Stitching of DSPF/SPEF/DPF Files                                                    | 444 |

| Post-Layout Simulation Methodologies                                                                           | 444 |

|----------------------------------------------------------------------------------------------------------------|-----|

| Static Power Grid Solver                                                                                       |     |

| SPGS Output                                                                                                    | 455 |

| Conversion Options                                                                                             | 456 |

|                                                                                                                |     |

| <u>14</u>                                                                                                      |     |

| <u>Encryption</u>                                                                                              | 459 |

| New key for Encryption                                                                                         |     |

| Encrypting a Netlist                                                                                           |     |

| What You can Encrypt                                                                                           |     |

| Encrypted Information During Simulation                                                                        |     |

| Protected Device                                                                                               |     |

| Protected Node                                                                                                 |     |

| Protected Global and Netlist Parameters                                                                        | 468 |

| Protected Subcircuit Parameters                                                                                |     |

| Protected Model Parameters                                                                                     | 468 |

| Multiple Name Spaces                                                                                           | 469 |

|                                                                                                                |     |

| <u>15</u>                                                                                                      |     |

| Time-Saving Techniques                                                                                         | 471 |

| Specifying Efficient Starting Points                                                                           |     |

| Reducing the Number of Simulation Runs                                                                         |     |

| Adjusting Speed and Accuracy                                                                                   |     |

| Saving Time by Starting Analyses from Previous Solutions                                                       |     |

| Saving Time by Specifying State Information                                                                    |     |

| Setting Initial Conditions for All Transient Analyses                                                          |     |

| Supplying Solution Estimates to Increase Speed                                                                 |     |

| Specifying State Information for Individual Analyses                                                           |     |

| Saving Time by Modifying Parameters during a Simulation                                                        |     |

| Changing Circuit or Component Parameter Values                                                                 |     |

| Modifying Initial Settings of the State of the Simulator                                                       |     |

| Saving Time by Selecting a Continuation Method                                                                 |     |

| OUVING THEO BY COLOUNING A CONTINUATION INSTITUTE THE TRANSPORT OF THE CONTINUATION OF THE CONTINUATION OF THE | 701 |

| <u>16</u>                                                 |

|-----------------------------------------------------------|

|                                                           |

| About Virtuoso Spectre Filename Specification             |

| Creating Filenames That Help You Manage Data              |

| Creating Filenames by Modifying Input Filenames           |

| Description of Spectre Predefined Percent Codes           |

| Customizing Percent Codes                                 |

| Creating Filenames from Parts of Input Filenames          |

| 17                                                        |

| Identifying Problems and Troubleshooting49                |

| Error Conditions                                          |

| Invalid Parameter Values That Terminate the Program       |

| Singular Matrices                                         |

| Internal Error Messages                                   |

| Time Is Not Strictly Increasing                           |

| Spectre Warning Messages                                  |

| P-N Junction Warning Messages                             |

| Tolerances Might Be Set Too Tight                         |

| Parameter Is Unusually Large or Small                     |

| gmin Is Large Enough to Noticeably Affect the DC Solution |

| Minimum Timestep Used                                     |

| <u>Syntax Errors</u>                                      |

| Topology Messages                                         |

| Model Parameter Values Clamped                            |

| Invalid Parameter Warnings                                |

| Redefine Primitives Messages                              |

| Initial Condition Messages                                |

| Output Messages                                           |

| Log File Messages 500                                     |

| Customizing Error and Warning Messages                    |

| Selecting Limits for Parameter Value Warning Messages     |

| Selecting Limits for Operating Region Warnings            |

| Range Checking on Subcircuit Parameters                   |

| Formatting the paramtest Component                                                       |            |

|------------------------------------------------------------------------------------------|------------|

| Controlling Program-Generated Messages                                                   |            |

| Specifying Log File Options                                                              |            |

| Correcting Convergence Problems                                                          |            |

| Correcting DC Convergence Problems                                                       |            |

| Correcting Transient Analysis Convergence Problems                                       |            |

| Correcting Accuracy Problems                                                             |            |

| Suggestions for Improving DC Analysis Accuracy                                           |            |

| Suggestions for Improving Transient Analysis Accuracy                                    |            |

| Packaging a Test Case for Shipment to Cadence                                            |            |

| Example                                                                                  | 51/        |

| <u>A</u>                                                                                 |            |

| Example Circuits                                                                         | 519        |

| Notes on the BSIM3v3 Model                                                               | 520        |